tc397学习资料

Infineon

相关资料:

开发板套件介绍页面:https://www.infineon.com/cms/en/product/evaluation-boards/kit_a2g_tc397_5v_tft/

开发板说明文档:Application Kit Manual TC3X7, ASCLIN_Shell_UART_1_KIT_TC397_TFT

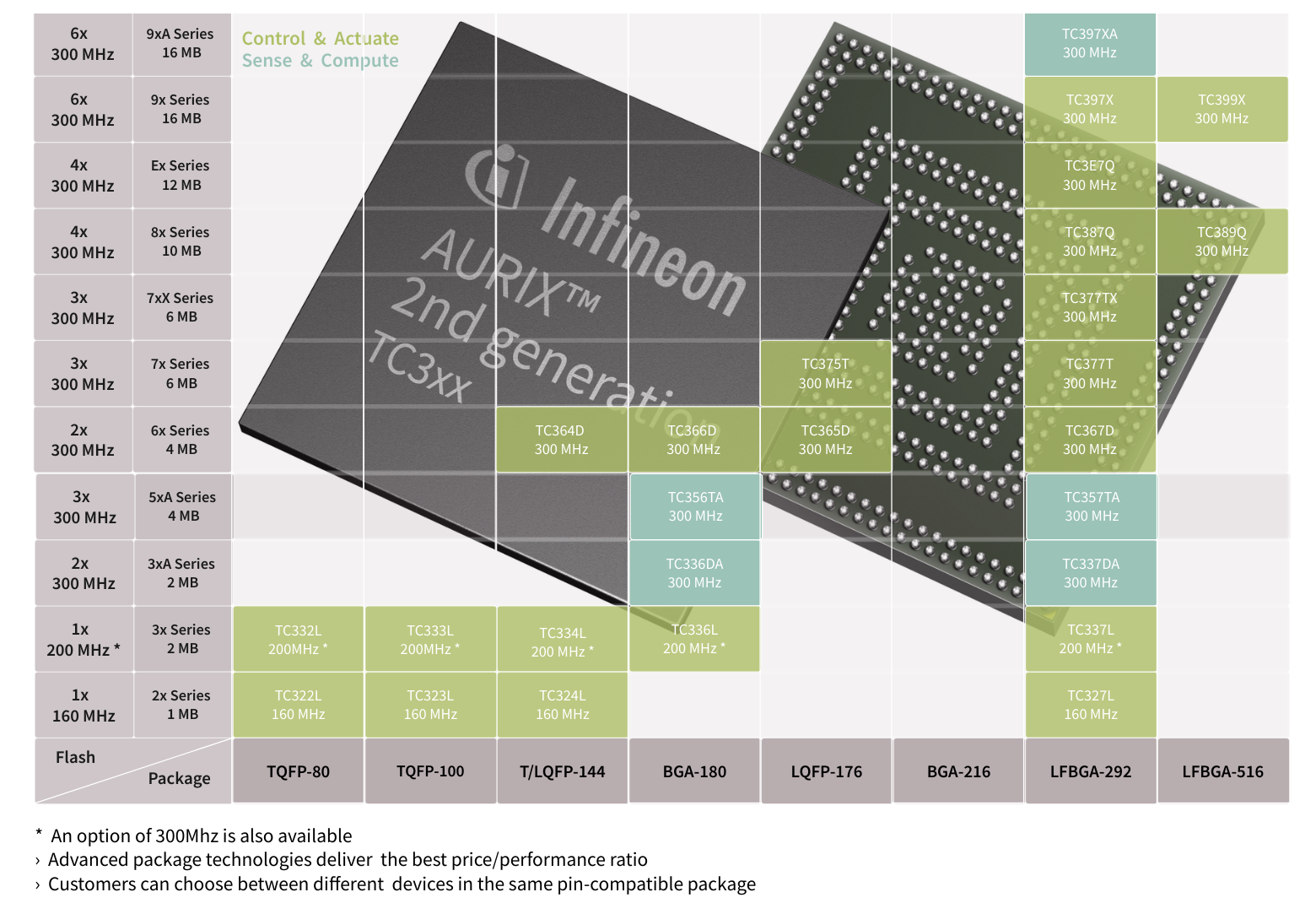

TC3xx系列总览: 32-bit TriCore™ AURIX™– TC3xx

用户手册: AURIX™ TC39x User Manual

示例代码: Infineon/AURIX_code_examples

英飞凌汽车电子生态圈:https://www.infineon.com/cms/cn/partners/partner-ecosystems/greater-china/autoeco/

选型:

搜索 Microcontroller pocket guide 文档

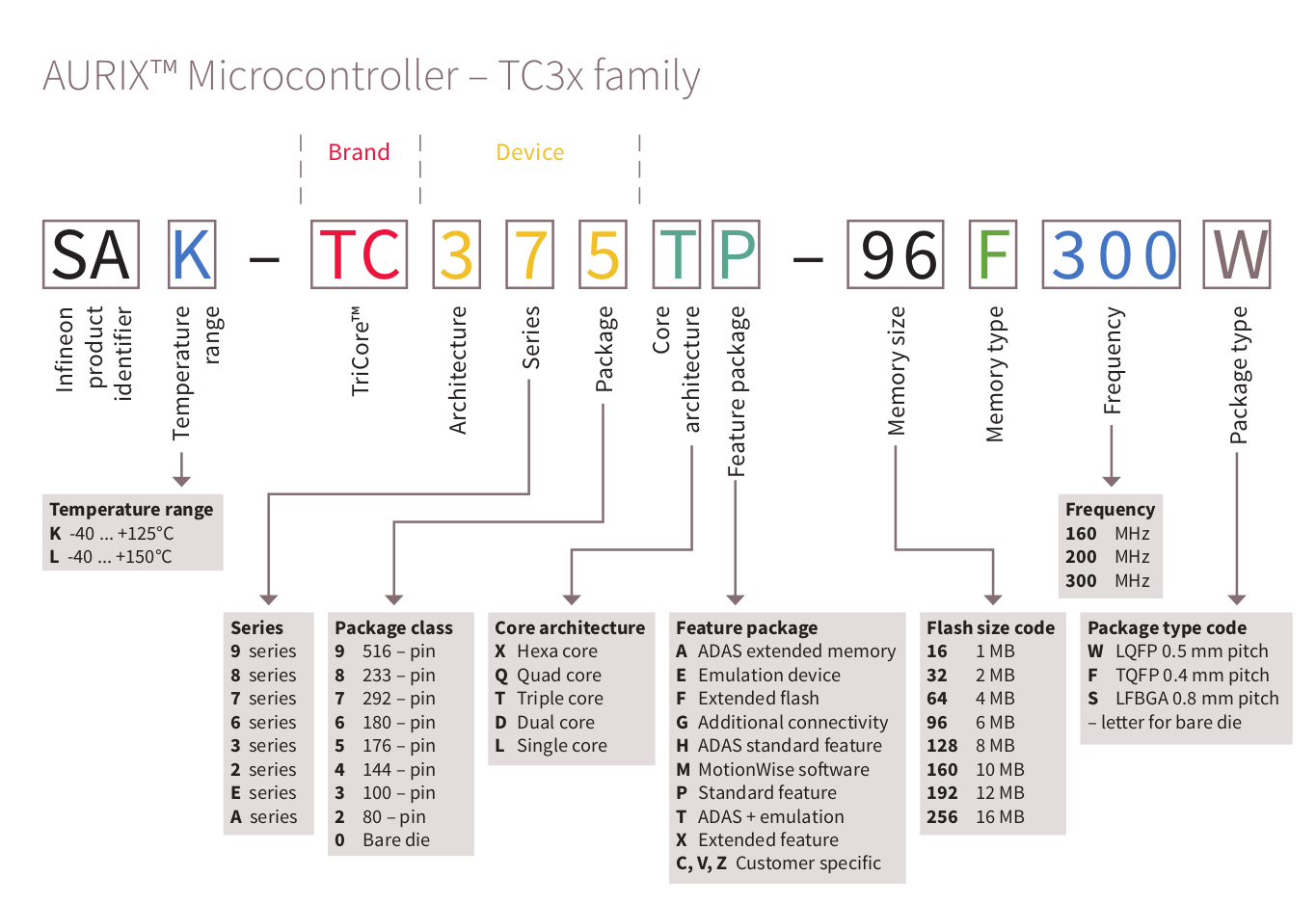

命令规则:

infineon-microcontroller-pocket-guide-2024-productselectionguide-en.pdf

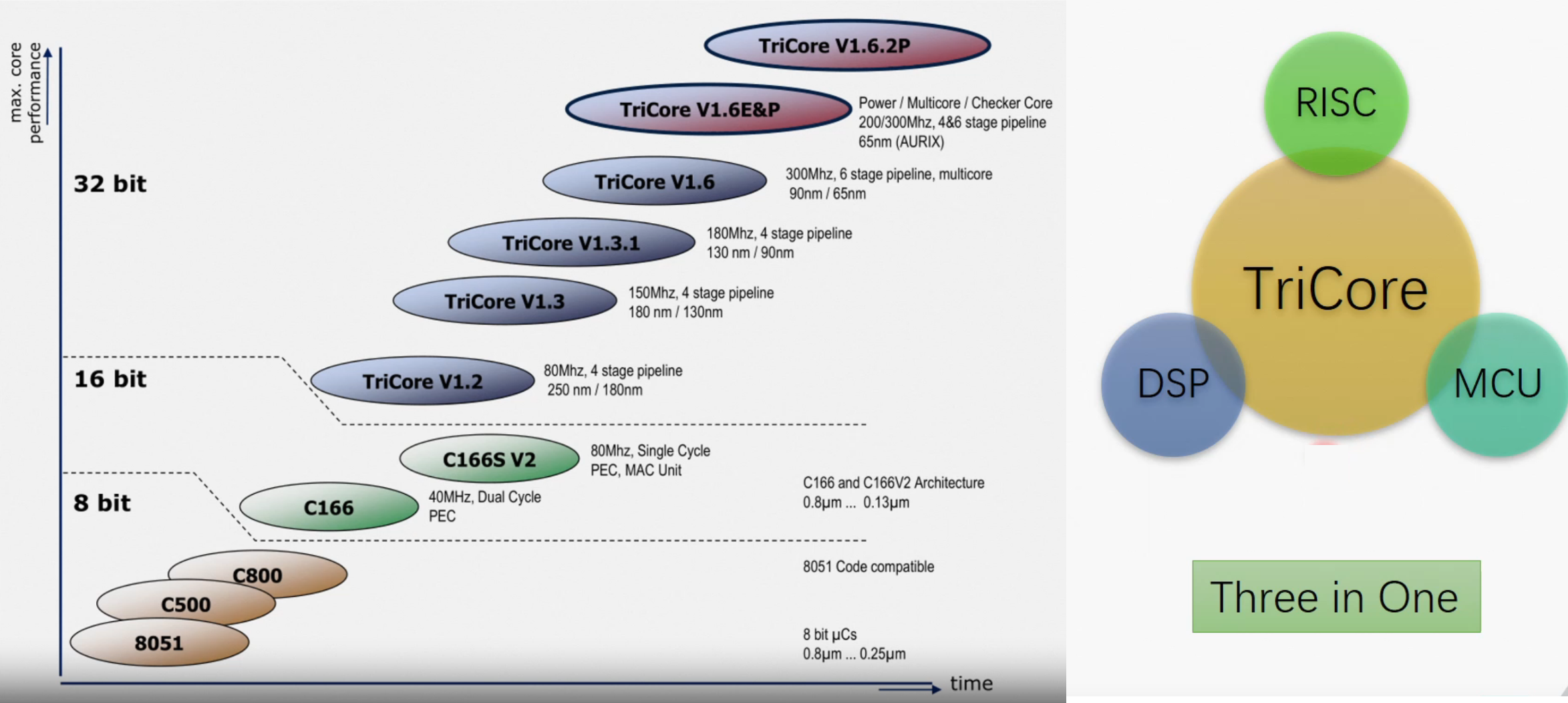

TriCore架构

Infineon-AURIX_TC3xx_Architecture_all-UserManual-v01_00-EN.pdf

TriCore是一种统一的、单核的32位微控制器-DSP架构,专为实时嵌入式系统优化。TriCore指令集架构(ISA)结合了微控制器的实时能力、DSP的计算能力和RISC加载/存储架构的高性能/价格特点,并且具有紧凑的可重编程核心

- 统一32位地址空间,包含可选的虚拟地址和内存映射I/O

- 支持16位和32位指令格式,16位指令是32位指令的子集,因其使用频率高才选择。这些指令显著减少了代码空间,降低了内存需求、系统和功耗

- 实时响应能力主要由中断延迟和上下文切换时间决定,避免长的多周期指令和提供灵活的硬件支持中断方案来最小化中断延迟

- 支持快速上下文切换

- 小端字节序:data memory and CPU registers

EABI传参

2.2.3 Argument Passing1

- 用于 非指针类型(例如 int, float, char 等) 的寄存器:

D4, D5, D6, D7

- 用于 指针类型(例如 char*, int*, struct* 等) 的寄存器:

A4, A5, A6, A7

CALL和RET自动保存/恢复这些寄存器:D8–D15, A10–A15

task切换只需手动保存lower context即可

返回值

2.2.5 Return Values

包括 int, float, char, bool 等类型

D2

64-bit 标量

- 使用

E2,即D2:D3

- 使用

32-bit 指针类型

- 使用

A2

- 使用

64-bit 指针

A2:A3

小于等于 32-bit 的结构体

D2

大小在 33 ~ 64-bit 的结构体

A2:A3

大于 64-bit 的结构体

调用者(caller)分配返回结构体所需的缓冲区

寄存器:

通用寄存器:32个

数据寄存器 (D[0] - D[15]): 用于存储和处理数据

地址寄存器 (A[0] - A[15]): 用于存储和操作内存地址

A[10]、A[11]、A[15]、D[15]这4个通用寄存器还有特殊功能:

A[10]:栈指针寄存器Stack Pointer (SP) register

A[11]:返回地址寄存器Return Address (RA) register

A[15]:隐式基地址寄存器Implicit Address register

D[15]:隐式数据寄存器Implicit Data register

A[0]、A[1]、A[8]、A[9]是系统全局寄存器:

函数调用、中断发生过程中,上下文的Save和Restore不会存储这4个寄存器中的信息

其他功能寄存器

- DEA (Data Error Address Register):记录触发异常的内存地址(对于数据访问异常,如空指针或写只读区域)

- DSTR (Data Synchronous Trap Register):提供数据访问异常的详细信息

- FCX (Free Context List Pointer):指向可用上下文保存区域,可能用于检查上下文是否耗尽(可能导致异常)

| Register Name | Description | AddressOffset |

|---|---|---|

| PCXI2 | Previous Context Information Register | FE00 |

| PSW3 | Program Status Word Register | FE04 |

| CPU_ID | CPU Identification Register (Read Only) | FE18 |

| CORE_ID | Core Identification Register | FE1C |

| BIV4 | Base Interrupt Vector Table Pointer | FE20 |

| BTV5 | Base Trap Vector Table Pointer | FE24 |

| ISP | Interrupt Stack Pointer Register | FE28 |

| ICR6 | ICU Interrupt Control Register | FE2C |

Trap System

处理各种异常事件,如不可屏蔽中断(NMI)、指令异常或非法访问,不能被软件屏蔽,trap一直是使能的

trap类型:

TriCore架构将陷阱分为八个类别,每个类别进一步分为同步或异步、硬件或软件陷阱。每个陷阱都有一个陷阱识别号(Trap Identification Number, TIN),用于在其类别内标识陷阱的原因。当陷阱被捕获时,陷阱识别号 TIN 会放置在数据寄存器D[15]中

D15的低六位中

- MMU (Memory Management Unit) 陷阱: 与内存管理单元相关的异常,如内存访问违例。

- 内部保护陷阱: 保护机制引发的异常,如权限问题。

- 指令错误陷阱: 指令执行过程中发生的错误,如非法指令。

- 上下文管理陷阱: 与任务上下文切换相关的异常。

- 系统总线和外设陷阱: 系统总线和外设引发的异常。

- 断言陷阱: 程序中断言失败引发的异常。

- 系统调用陷阱: 系统调用指令引发的异常。

- 不可屏蔽中断 (NMI) 陷阱: 高优先级的不可屏蔽中断引发的异常。

又可分为如下几种类型:

- 同步陷阱: 由指令执行过程中的错误引发,发生在程序的预定点。

- 异步陷阱: 由外部事件(如中断)引发,可能在程序执行的任意时刻发生。

- 硬件陷阱: 由硬件错误或异常引发。

- 软件陷阱: 由软件错误或异常引发。

- 不可恢复的陷阱: 引发任务不可恢复,无法简单重新启动。

| TIN | Name | Synch./ ASynch. | HW/ SW | Definition |

|---|---|---|---|---|

| Class 0 | — | — | — | MMU |

| 0 | VAF | Synch. | HW | Virtual Address Fill. |

| 1 | VAP | Synch. | HW | Virtual Address Protection. |

| Class 1 | — | — | — | Internal Protection Traps |

| 1 | PRIV | Synch. | HW | Privileged Instruction. |

| 2 | MPR | Synch. | HW | Memory Protection Read. |

| 3 | MPW | Synch. | HW | Memory Protection Write. |

| 4 | MPX | Synch. | HW | Memory Protection Execution. |

| 5 | MPP | Synch. | HW | Memory Protection Peripheral Access. |

| 6 | MPN | Synch. | HW | Memory Protection Null Address. |

| 7 | GRWP | Synch. | HW | Global Register Write Protection. |

| Class 2 | — | — | — | Instruction Errors |

| 1 | IOPC | Synch. | HW | Illegal Opcode. |

| 2 | UOPC | Synch. | HW | Unimplemented Opcode. |

| 3 | OPD | Synch. | HW | Invalid Operand specification. |

| 4 | ALN | Synch. | HW | Data Address Alignment. |

| 5 | MEM | Synch. | HW | Invalid Local Memory Address. |

| Class 3 | — | — | — | Context Management |

| 1 | FCD | Synch. | HW | Free Context List Depletion (FCX = LCX). |

| 2 | CDO | Synch. | HW | Call Depth Overflow. |

| 3 | CDU | Synch. | HW | Call Depth Underflow |

| 4 | FCU | Synch. | HW | Free Context List Underflow (FCX = 0). |

| 5 | CSU | Synch. | HW | Call Stack Underflow (PCX = 0). |

| 6 | CTYP | Synch. | HW | Context Type (PCXI.UL wrong). |

| 7 | NEST | Synch. | HW | Nesting Error: RFE with non-zero call depth. |

| Class 4 | — | — | — | System Bus and Peripheral Errors |

| 1 | PSE | Synch. | HW | Program Fetch Synchronous Error. |

| 2 | DSE | Synch. | HW | Data Access Synchronous Error. |

| 3 | DAE | Asynch | AHW | Data Access Asynchronous Error. |

| 4 | CAE | Asynch | HW | Coprocessor Trap Asynchronous Error. |

| 5 | PIE | Synch | HW | Program Memory Integrity Error. |

| 6 | DIE | Asynch | HW | Data Memory Integrity Error. |

| 7 | TAE | Asynch | HW | Temporal Asynchronous Error |

| Class 5 | — | — | — | Assertion Traps |

| 1 | OVF | Synch | SW | Arithmetic Overflow. |

| 2 | SOVF | Synch | SW | Sticky Arithmetic Overflow. |

| Class 6 | — | — | — | System Call |

| SYS | Synch | SW | System Call. | |

| Class 7 | — | — | — | Non-Maskable Interrupt |

| 0 | NMI | Asynch | HW | Non-Maskable Interrupt |

Infineon-AURIX_TC3xx_Architecture_vol1-UserManual-v01_00-EN_merged_unsigned.pdf -> 6.1 Trap Types

异常处理:

陷阱不会改变 CPU 的中断优先级,因此 ICR.CCPN 字段不会被更新

返回地址存储在返回地址寄存器 A[11] 中。

同步陷阱,返回地址是引发陷阱的指令的程序计数器 (PC)

SYS 陷阱: 由 SYSCALL 指令触发的 SYS 陷阱,返回地址指向 SYSCALL 之后的指令

FCD 陷阱: 详见 “FCD - 自由上下文列表耗尽 (TIN 1)”

异步陷阱: 返回地址是如果未发生陷阱将要执行的下一条指令地址。中断的返回地址也遵循相同的规则

当发生陷阱时,硬件会生成一个陷阱标识符,该标识符由两个部分组成:

- 陷阱类别号 (TCN): 用于索引到陷阱向量表。

- 陷阱识别号 (TIN): 该号码会被加载到数据寄存器

D[15]中。

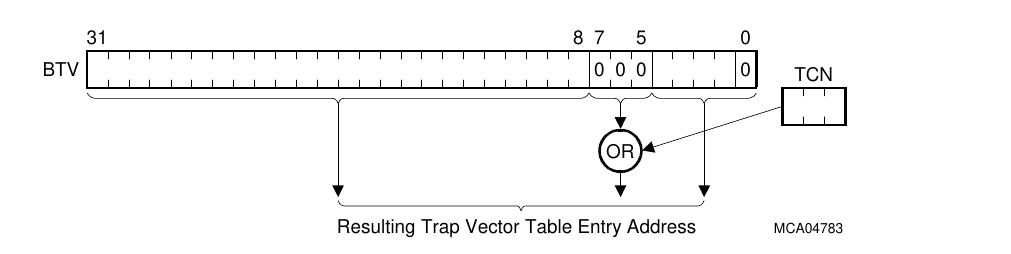

陷阱类别号 (TCN) 会左移五位,并与 BTV 寄存器中的地址进行按位或操作,以生成陷阱处理程序的入口地址。

异常向量基地址 :BTV, 每两个之间间隔32个byte ,如果处理逻辑很简短,可以放在向量代码段32个byte内,否则就跳到处理程序其他部分,使用 MTCR 指令修改 BTV 寄存器,有多个异常向量表的时候可以适配调整。

通过TCN左移5位与上BTV,找到函数的入口地址

Unlike the Interrupt Vector Table, entries in the Trap Vector Table cannot be spanned. 所有的trap条目都要配置 ?

TCN的作用,计算配置trap向量表,找到入口地址,然后TIN进行处理?

陷阱触发时的初始状态

当陷阱发生时的初始状态定义如下:

- 上层上下文被保存。

- 返回地址更新至

A[11]。 - 陷阱识别号 (TIN) 被加载到

D[15]。 - 堆栈指针 (A[10]) 被设置为中断堆栈指针 (ISP),前提是处理器之前未使用中断堆栈(即

PSW.IS = 0)。堆栈指针位被设置为使用中断堆栈:PSW.IS = 1。 - I/O 模式被设置为监督模式,这意味着所有权限都被启用:

PSW.IO = 10B。 - 当前保护寄存器组被设置为

0:PSW.PRS = 000B。 - 调用深度计数器 (CDC) 被清零,调用深度限制设置为 64:

PSW.CDC = 0000000B。 - 启用调用深度计数器,

PSW.CDE = 1。 - PSW 安全位被设置为

SYSCON寄存器中定义的值:PSW.S = SYSCON.TS。 - 禁止写入全局寄存器

A[0],A[1],A[8],A[9]:PSW.GW = 0。 - 中断系统被全局禁用:

ICR.IE = 0。旧的ICR.IE和ICR.CCPN分别保存到PCXI.PIE和PCXI.PCPN中。ICR.CCPN保持不变。 - 访问陷阱向量表以获取陷阱处理程序的第一条指令。

**尽管陷阱不会更改 ** ICR.CCPN ,但它们的处理程序仍然在中断被禁用的情况下开始执行。因此,它们可以在不被中断的情况下执行关键的初始操作,直到它们明确重新启用中断。

对于不可恢复的 FCU 陷阱,初始状态有所不同。上层上下文无法保存。只有以下状态被保证:

- TIN 被加载到

D[15]。 - 堆栈指针 (A[10]) 被设置为中断堆栈指针 (ISP),前提是处理器之前未使用中断堆栈(即

PSW.IS == 0)。 - I/O 模式被设置为监督模式(所有权限都被启用:

PSW.IO = 10B)。 - 当前保护寄存器组被设置为

0:PSW.PRS = 000B。 - PSW 安全位被设置为

SYSCON寄存器中定义的值:PSW.S = SYSCON.TS。 - 中断系统被全局禁用:

ICR.IE = 0。ICR.CCPN保持不变。 - 访问陷阱向量表以获取 FCU 陷阱处理程序的第一条指令

代码分析

BTV寄存器设置trap异常跳转函数

1#define TRAPTAB0 (LCF_TRAPVEC0_START)

2group trapvec_tc0 (align = 8, run_addr=LCF_TRAPVEC0_START)

3{

4 section "trapvec_tc0" (size=0x100, attributes=rx, fill=0)

5 {

6 select "(.text.traptab_cpu0*)";

7 }

8}

9"__TRAPTAB_CPU0" := TRAPTAB0;

10#define CPU_BTV 0xFE24

11#define __TRAPTAB_CPU(cpu) __TRAPTAB_CPU##cpu

12#define __TRAPTAB(cpu) __TRAPTAB_CPU##cpu

13Ifx_Ssw_MTCR(CPU_BTV, (unsigned int)__TRAPTAB(0));

14

15

16#pragma ghs section text=".traptab_cpu0"

17void IfxCpu_Trap_vectorTable0(void)

18{

19 IfxCpu_Tsr_CallTSR(IfxCpu_Trap_memoryManagementError);

20 IfxCpu_Tsr_CallTSR(IfxCpu_Trap_internalProtectionError);

21 IfxCpu_Tsr_CallTSR(IfxCpu_Trap_instructionError);

22 IfxCpu_Tsr_CallCSATSR(IfxCpu_Trap_contextManagementError);

23 IfxCpu_Tsr_CallTSR(IfxCpu_Trap_busError);

24 IfxCpu_Tsr_CallTSR(IfxCpu_Trap_assertion);

25 IfxCpu_Tsr_CallTSR(IfxCpu_Trap_systemCall_Cpu0);

26 IfxCpu_Tsr_CallTSR(IfxCpu_Trap_nonMaskableInterrupt);

27}

28#pragma ghs section

29

30// defined(__ghs__)

31#define __ALIGN_TRAP_TAB__ __asm(" .align 32");

32#define IfxCpu_Tsr_CallTSR(serviceRoutine) \

33 { \

34 __ALIGN_TRAP_TAB__; \

35 __asm("svlcx\n"); \

36 __asm("mov\t d4, d15"); \

37 __asm("ji\t %0" : : "a" (serviceRoutine)); \

38 __asm("rfe"); \

39 }

40#define IfxCpu_Tsr_CallCSATSR(serviceRoutine) \

41 { \

42 __ALIGN_TRAP_TAB__; \

43 __asm("mov\t d4, d15"); \

44 __asm("ji\t %0" : : "a" (serviceRoutine)); \

45 __asm("rfe"); \

46 }中断:

SRPN (Service Request Priority Number): 每个中断源分配一个唯一的 SRPN

PIPN (Pending Interrupt Priority Number) : 挂起中断优先级号

CCPN (Current CPU Priority Number): 当前cpu优先级

ICU (Interrupt Control Unit ): 中断控制单元

中断描述:

中断控制单元 (ICU) 使用 SRPN 来优先处理多个并发的中断请求。获胜请求的 SRPN 作为挂起中断优先级号 (PIPN),当有新的中断请求触发,CPU 通过将 PIPN 与当前 CPU 优先级号 (CCPN) 进行比较,决定是否接受请求的中断。如果 CPU 决定接受中断请求,它将响应一个中断确认,并返回已接受中断的优先级号。ICU 随后会清除请求的中断源

**中断响应条件: **ICR.IE == 1 && PIPN > CCPN

可能禁止中断响应的条件:

中断系统全局禁用 (ICR.IE == 0)。

当前 CPU 优先级 (CCPN) 等于或高于挂起中断优先级号 (PIPN)。

CPU 正在进入中断或陷阱服务例程。

CPU 正在执行不可中断的陷阱服务。

CPU 正在执行多周期指令。

CPU 正在执行修改 ICR 的指令

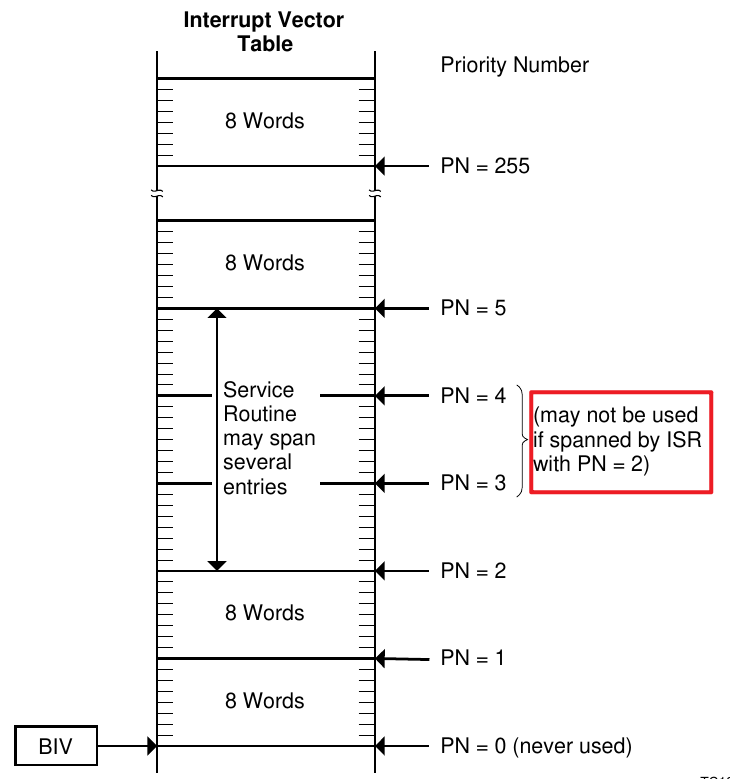

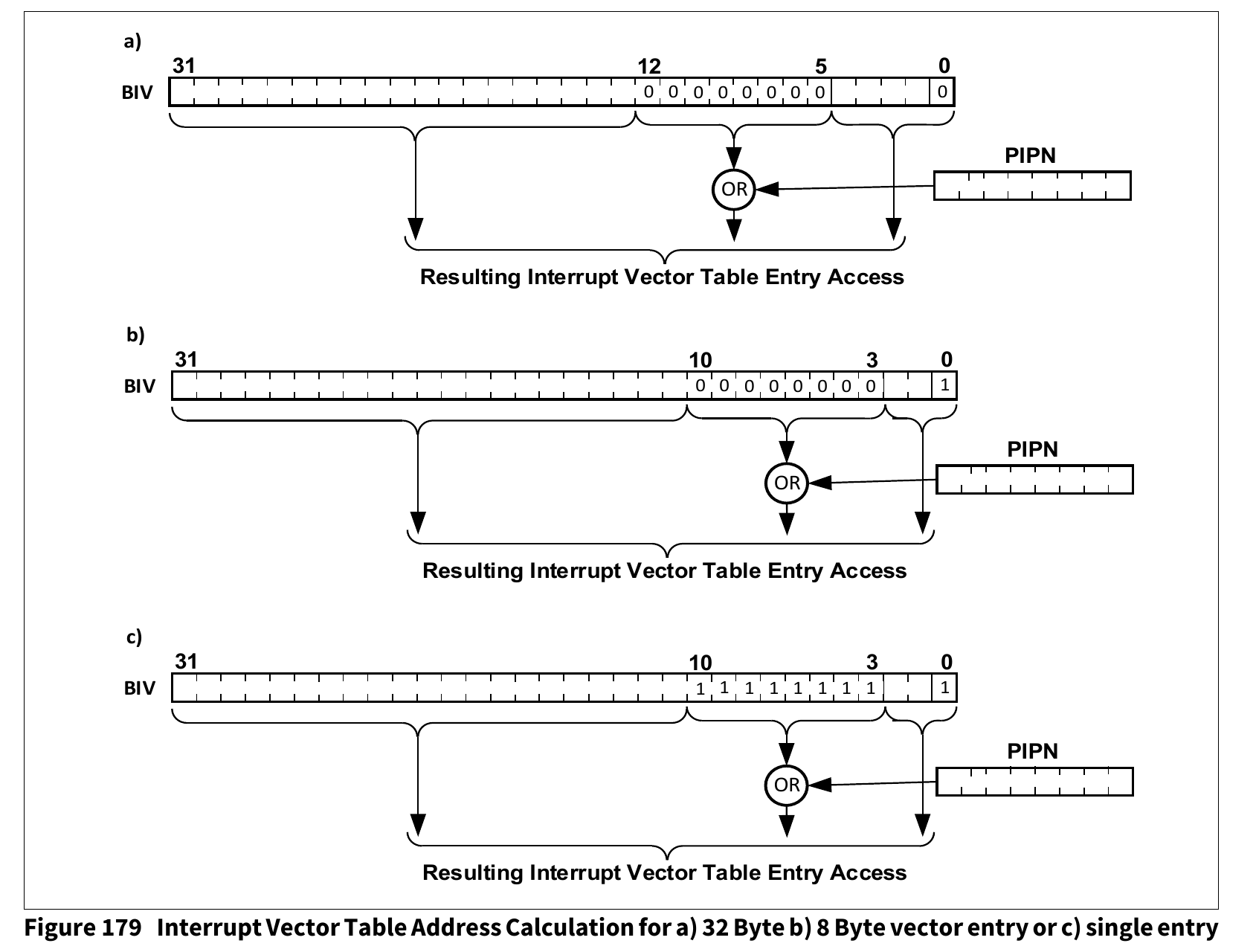

中断向量表:

每个中断向量占用32byte或者8byte,由BIV.VSS的值决定

1if (BIV.VSS == 1’b0)

2 ISR_Entry_PC = {BIV[31:1],1’b0} | {PIPN<<5};

3else

4 ISR_Entry_PC = {BIV[31:1],1’b0} | {PIPN<<3};

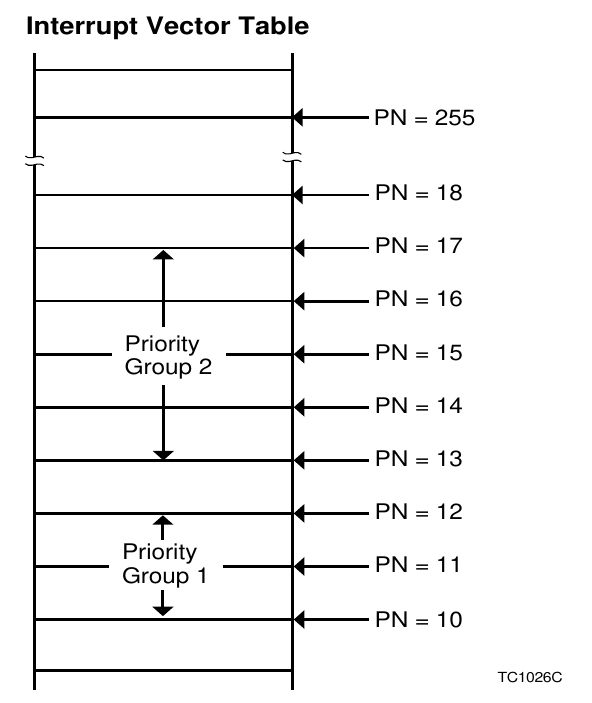

优先级组:

中断优先级组描述了一组不能中断彼此服务程序的中断。当 CPU 开始处理某个中断时,中断系统会被全局禁用,且 CPU 的当前优先级号码 (CCPN) 设置为正在服务的中断的优先级号码。这会阻止所有进一步的中断服务,直到通过软件重新启用中断系统或使用 RFE(异常返回)指令终止服务例程。

RFE 指令:RFE 指令会自动恢复 ICR.IE 位的前一个状态(ICR.IE = 1)

当 ISR 软件通过设置 ICR.IE 再次启用中断系统而不改变 CCPN 时,就可以阻止所有与 CCPN 相同或更低优先级的中断请求。这包括当前中断的重新发生,即当前中断不能中断自己的服务。但会被更高优先级的中断打断。为了实现中断优先级组,相关的服务例程软件会在再次启用中断系统之前, 将 CCPN 设置为该组中最高 SRPN 的值 ,如下图:

组1:11-12,CCPN=12

组2:14-17,CCPN=17

中断优先级:

中断处理:

进入中断的行为如下:

- The upper context of the current task is saved.

- The Return Address (A[11]) is updated with the current PC.

- If the processor was not previously using the interrupt stack (PSW.IS = 0), then the A[10] Stack Pointer is set to the interrupt stack pointer (ISP). The stack pointer bit is then set for using the interrupt stack: PSW.IS = 1.

- The I/O mode is set to Supervisor mode, which means all permissions are enabled: PSW.IO = 10B.

- The current Protection Register Set is set to 0: PSW.PRS = 000B.

- The Call Depth Counter (PSW.CDC) is cleared, and the call depth limit selector is set for 64: PSW.CDC = 0000000B. Call Depth Counter is enabled, PSW.CDE = 1.

- PSW Safety bit is set to value defined in the SYSCON register. PSW.S = SYSCON.IS.

- Write permission to global registers A[0], A[1], A[8], A[9] is disabled: PSW.GW = 0.

- The interrupt system is globally disabled: ICR.IE = 0. The old ICR.IE is saved into PCXI.PIE.

- The Current CPU Priority Number (ICR.CCPN) is saved into the Previous CPU Priority Number (PCXI.PCPN) field.

- The Pending Interrupt Priority Number (ICR.PIPN) is saved into the Current CPU Priority Number (ICR.CCPN) field.

- The interrupt vector table is accessed to fetch the first instruction of the ISR.

中断退出的行为:

- PCXI.PCPN is written to ICR.CCPN to set the CPU priority number to the value before interruption.

- PCXI.PIE is written to ICR.IE to restore the state of this bit.

任务切换

在嵌入式和实时控制系统设计中,通常将中断处理程序和软件管理的任务视为在各自的“虚拟”微控制器上执行。这个模型通常由实时执行系统或实时操作系统(RTOS)支持,这些系统层叠在底层机器架构的功能之上。

在TriCore™架构中,RTOS层需要处理的更少,硬件可以高效地处理任务之间的切换。同时,该架构允许在任务模型中具有相当大的灵活性。系统设计人员可以根据应用程序的需求选择最合适的实时执行系统和软件设计方法,而架构对其施加的限制相对较少。

在TriCore架构中,低开销的任务切换和函数调用机制是密切相关的。

任务切换,保护当前任务的上下文,然后回复另一个待执行任务的上下文,并执行

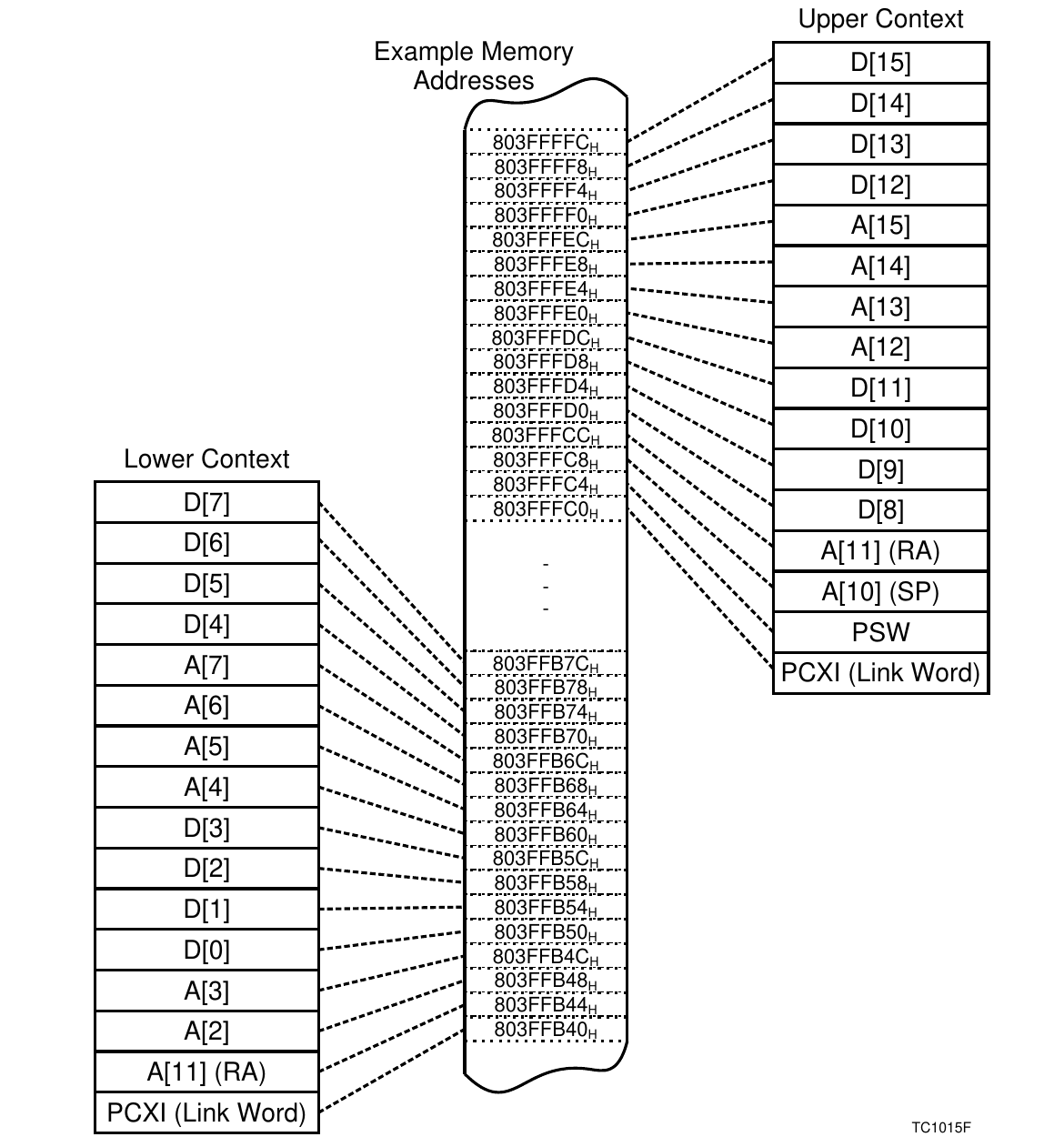

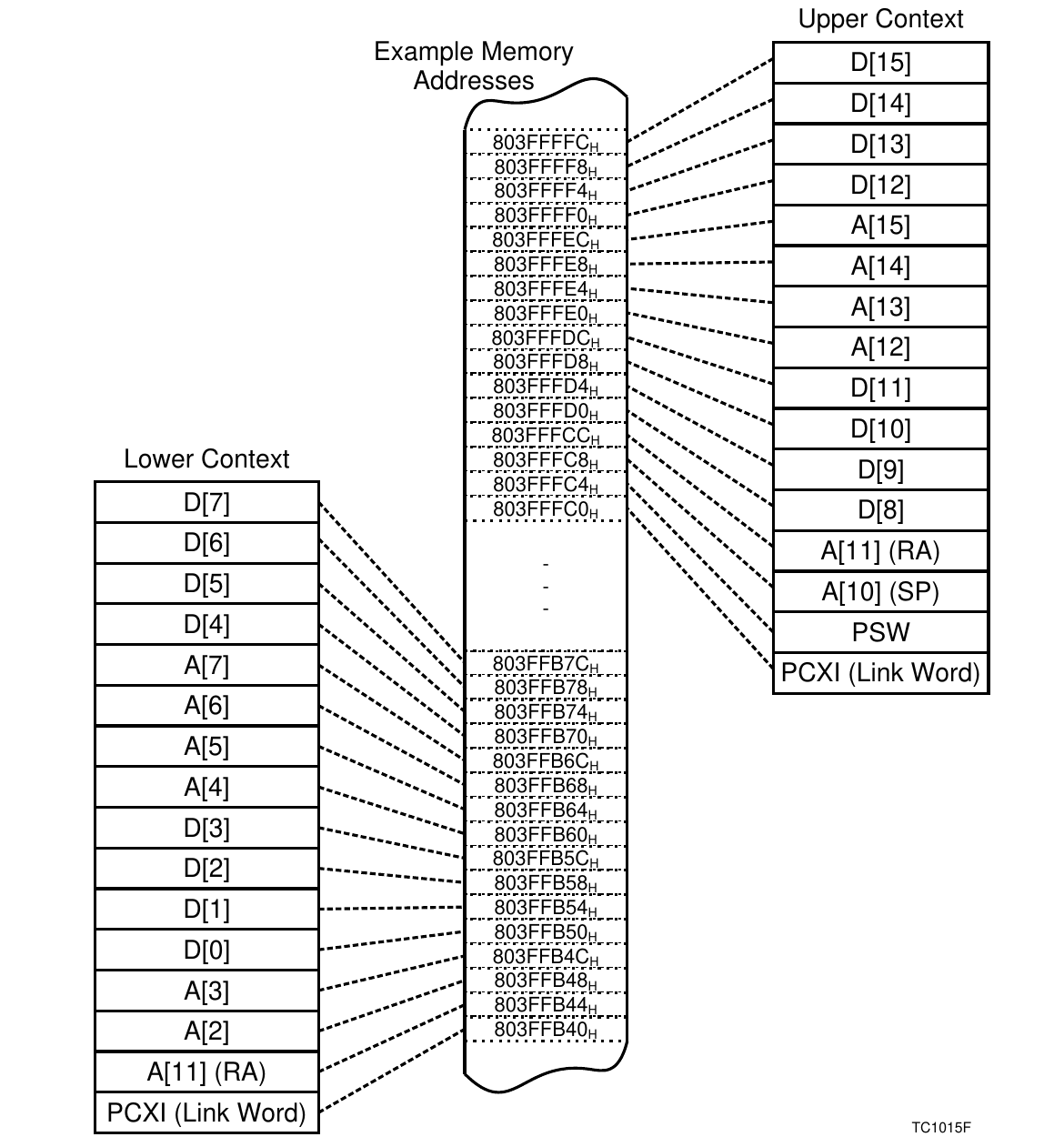

Contexts, when saved to memory, occupy 16 word blocks of storage, known as **Context Save Areas ** (CSAs).

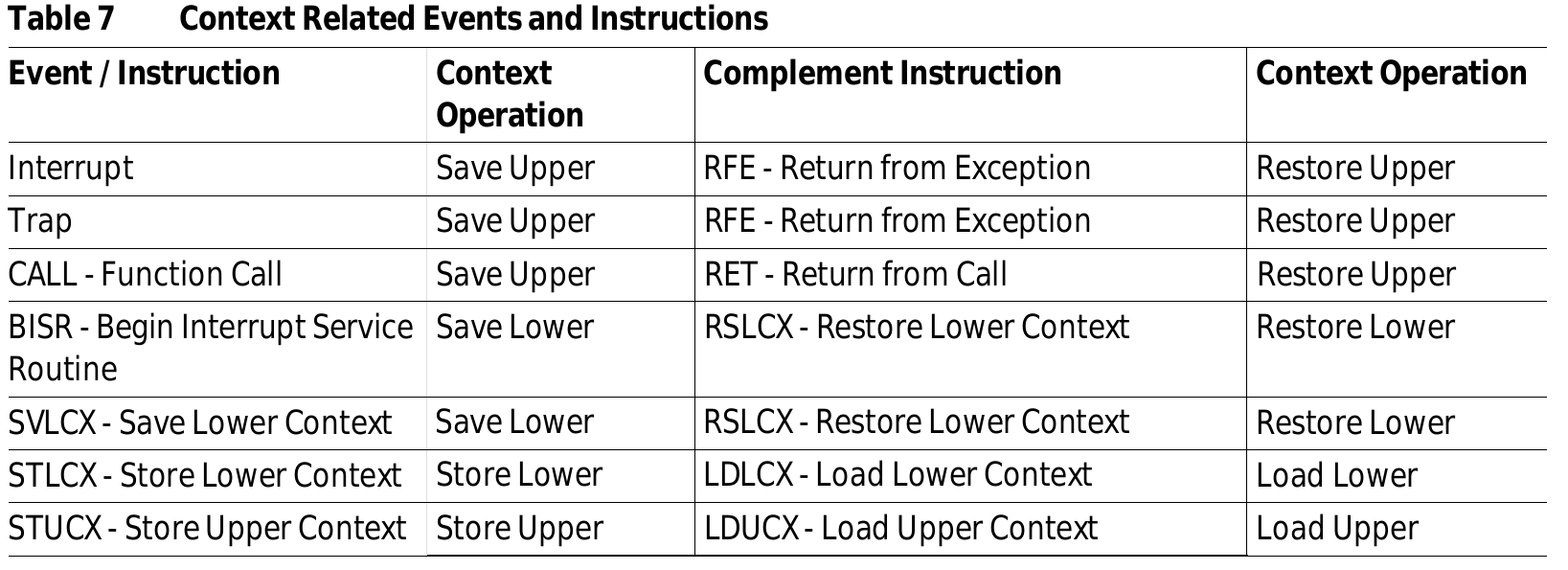

Upper context: 包括地址寄存器A[10]到A[15]和数据寄存器D[8]到D[15],PCXI和PSW。

Lower context : 包括地址寄存器A[2]到A[7]、数据寄存器D[0]到D[7]、A[11](返回地址)和PCXI。

每个CSA保存一个 Upper context 或 Lower context

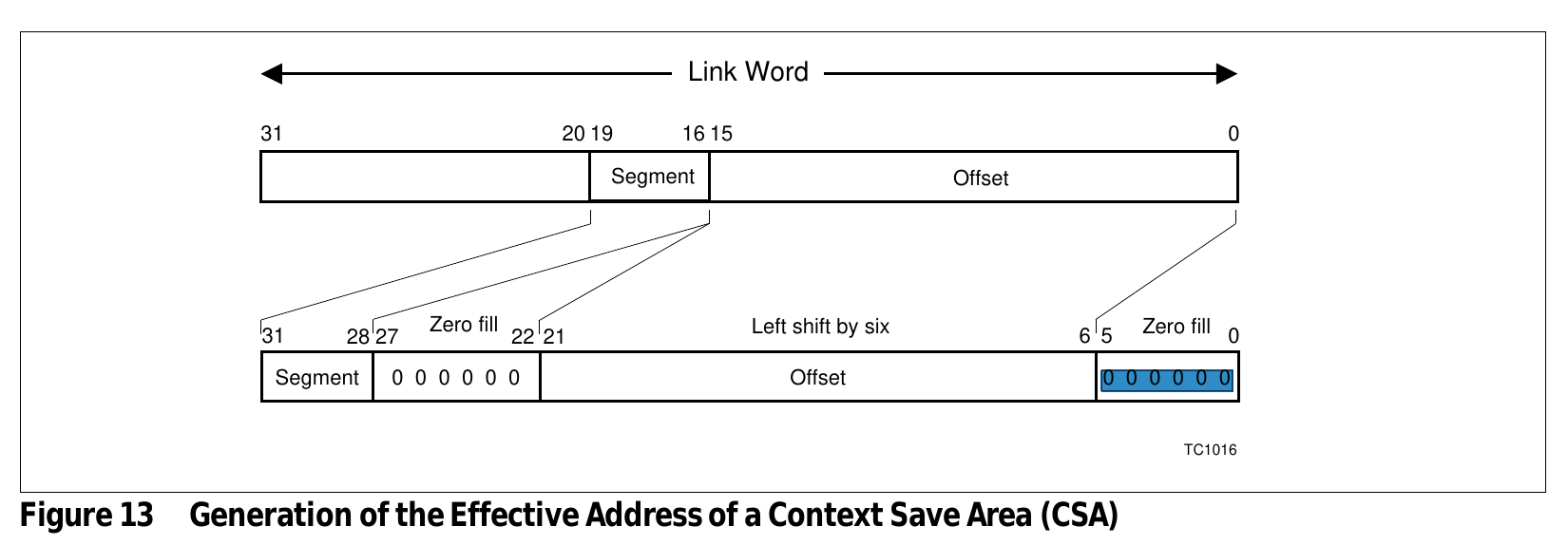

Link Word由两部分组成,Segment和Offset,上面解释了一个CSA占用64byte大小,所有CSA可用的大小是4M

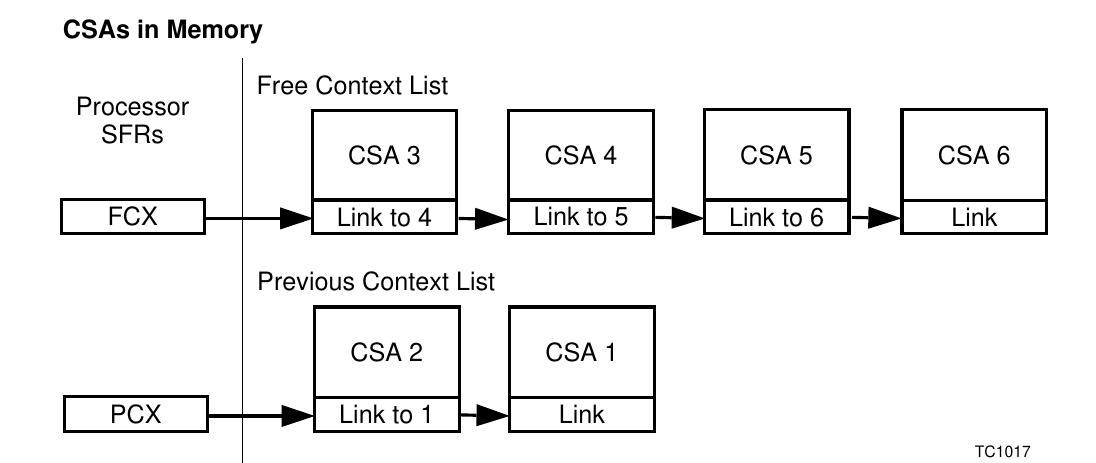

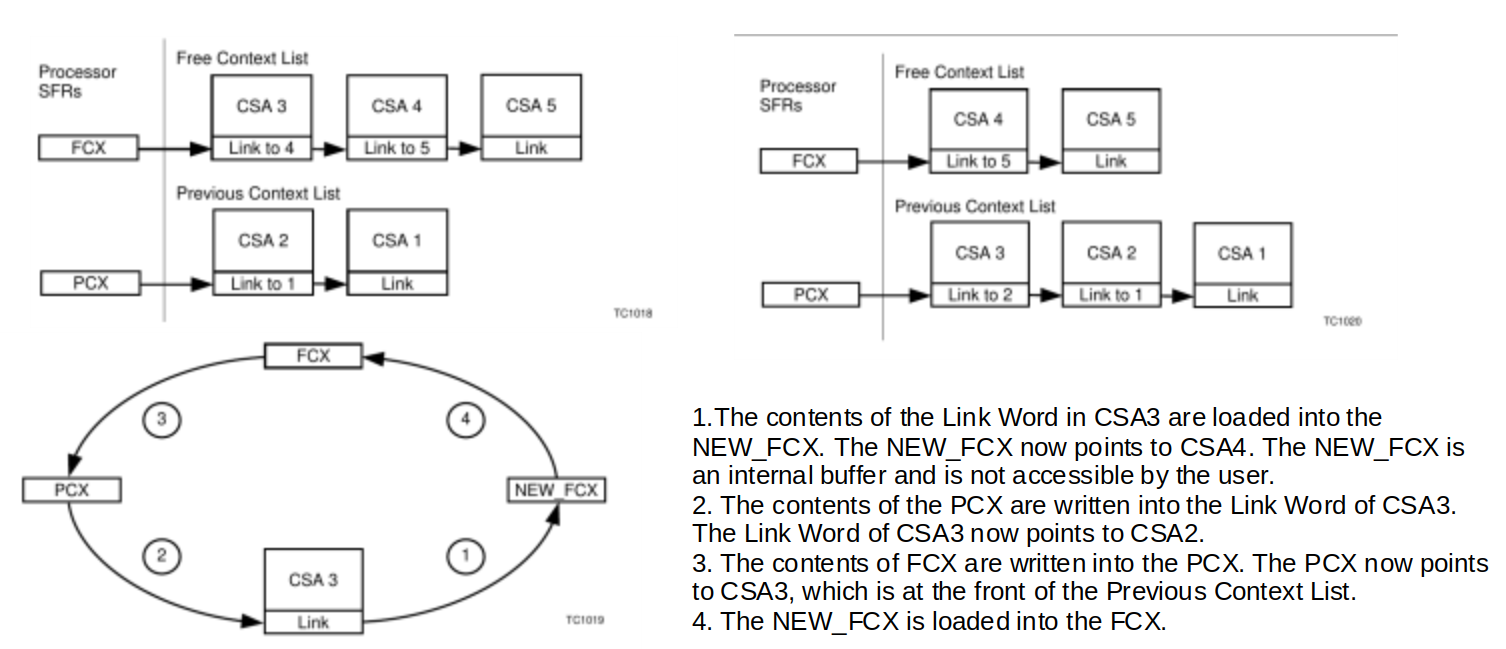

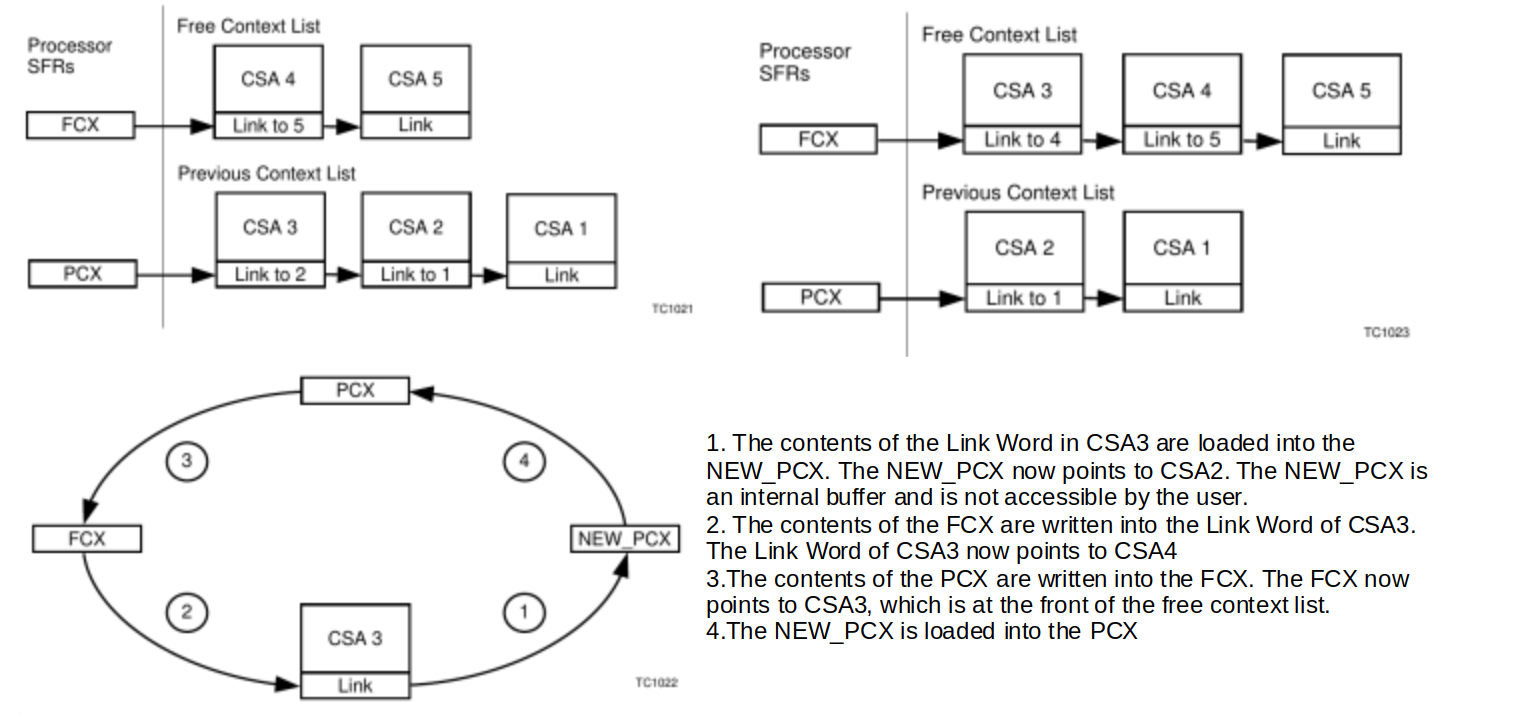

系统中的会维护两个CSA链表,Previous Context List (PCX) 和 Free Context List (FCX)

上下文保存:

- 下半部分上下文寄存器:类似于全局寄存器,即中断处理程序、陷阱处理程序或调用函数可以看到这些寄存器中断前的值。在事件结束后,这些寄存器中的任何更改会保留,因此可以用于 传递函数参数和返回值 。中断和陷阱处理程序必须在使用这些寄存器之前保存它们的原始值,并在退出之前恢复这些值。

- 上半部分上下文寄存器:这些寄存器不是硬件静态寄存器。概念上,函数调用或中断处理程序总是以自己私有的上半部分上下文寄存器开始执行。被中断或调用的函数的上半部分上下文寄存器不会被继承

- 只有 A10(sp)、A11(RA)、PSW、PCXI 和在陷阱情况下的 D[15] 寄存器在调用函数、陷阱处理程序或中断处理程序中具有架构定义的初始值。函数、陷阱处理程序或中断处理程序在写入其他上半部分上下文寄存器之前读取这些寄存器的值,是未定义操作。

上下文保存:

上下文恢复:

1/* 第一个 CSA */

2uppercontext = (uppercontext_t)LINKWORDTOEA(Fcx);

3/* 第二个 CSA */

4lowercontext = (lowercontext_t)LINKWORDTOEA(uppercontext->PCXI);

5/* 第三个 CSA 线程退出 */

6exitcontext = (uppercontext_t)LINKWORDTOEA(lowercontext->PCXI);模式与访问权限:

- 用户模式(User Mode)

- User-0模式: 该模式用于不访问外设的任务。在这个模式下,任务无法启用或禁用中断。

- User-1模式: 该模式用于访问常见的、未保护的外设任务。例如,串口读写操作、计时器的读操作,以及大多数I/O状态寄存器的访问。此模式下的任务可以禁用中断(此行为可以通过系统控制寄存器覆盖)。

- 监督模式(Supervisor Mode)

- 该模式允许任务读取和写入系统寄存器,并访问所有外设设备。此模式下的任务可以禁用中断。

Memory Barrier

内存屏障(Memory Barrier),也叫内存栅栏,是一种用于控制 CPU 和编译器在执行操作时的顺序的机制。内存屏障确保某些操作在代码执行顺序上保持一致,从而避免因指令重排序导致的不一致性问题。

内存屏障的作用

在多核系统中,不同核心可能会乱序执行指令或者 乱序读取/写入内存 。如果没有内存屏障,以下问题可能会发生:

- 数据竞争:两个核心同时访问同一内存位置,其中一个核心写入数据后,另一个核心可能会读到旧的数据。

- 指令重排序:编译器或 CPU 出于优化目的,可能会改变指令执行顺序,导致预期的同步行为被破坏。

内存屏障通过阻止这种乱序操作,确保所有核心看到一致的数据和内存操作顺序。

DSYNC(Data Synchronization)

- DSYNC 指令保证在 DSYNC 指令之前的所有数据访问操作都已完成,然后才会启动与 DSYNC 之后的指令相关联的任何数据内存访问操作。这包括所有对系统总线和本地数据内存的访问。

ISYNC(Instruction Synchronization)

ISYNC指令用于确保 CPU 内部的状态一致性。它主要用于指令的同步,确保在ISYNC指令之前的所有指令都已执行完毕,并且对架构状态的任何更改已经生效,然后才会继续执行ISYNC之后的指令。- ISYNC 指令的操作如下:

- 等待 ISYNC 之前的所有指令完成。

- 刷新 CPU 管道并取消 ISYNC 之后的所有指令。

- 使管道中所有缓存状态失效,例如循环缓存缓冲区。

- 重新获取 ISYNC 之后的下一条指令。

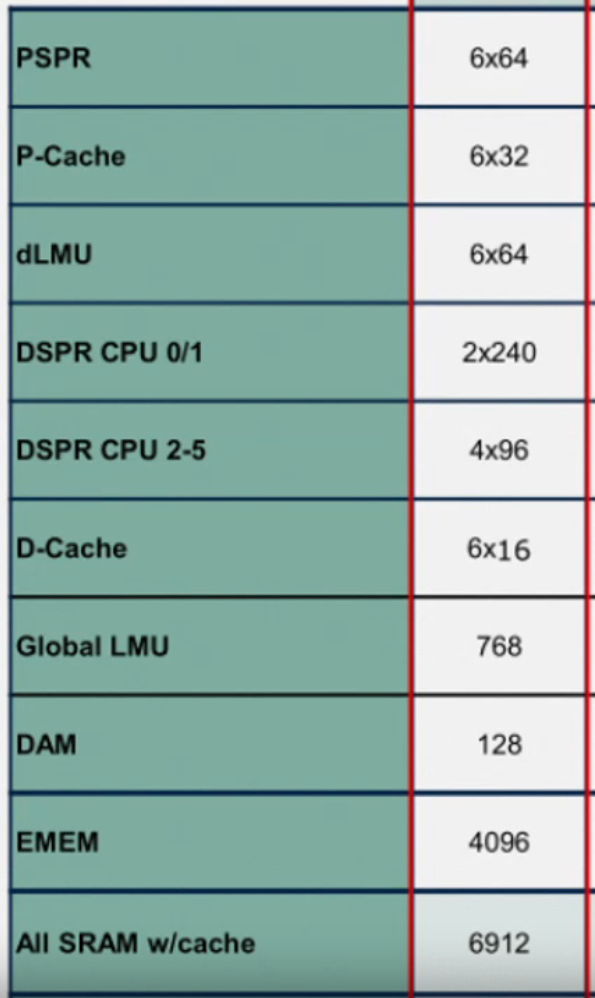

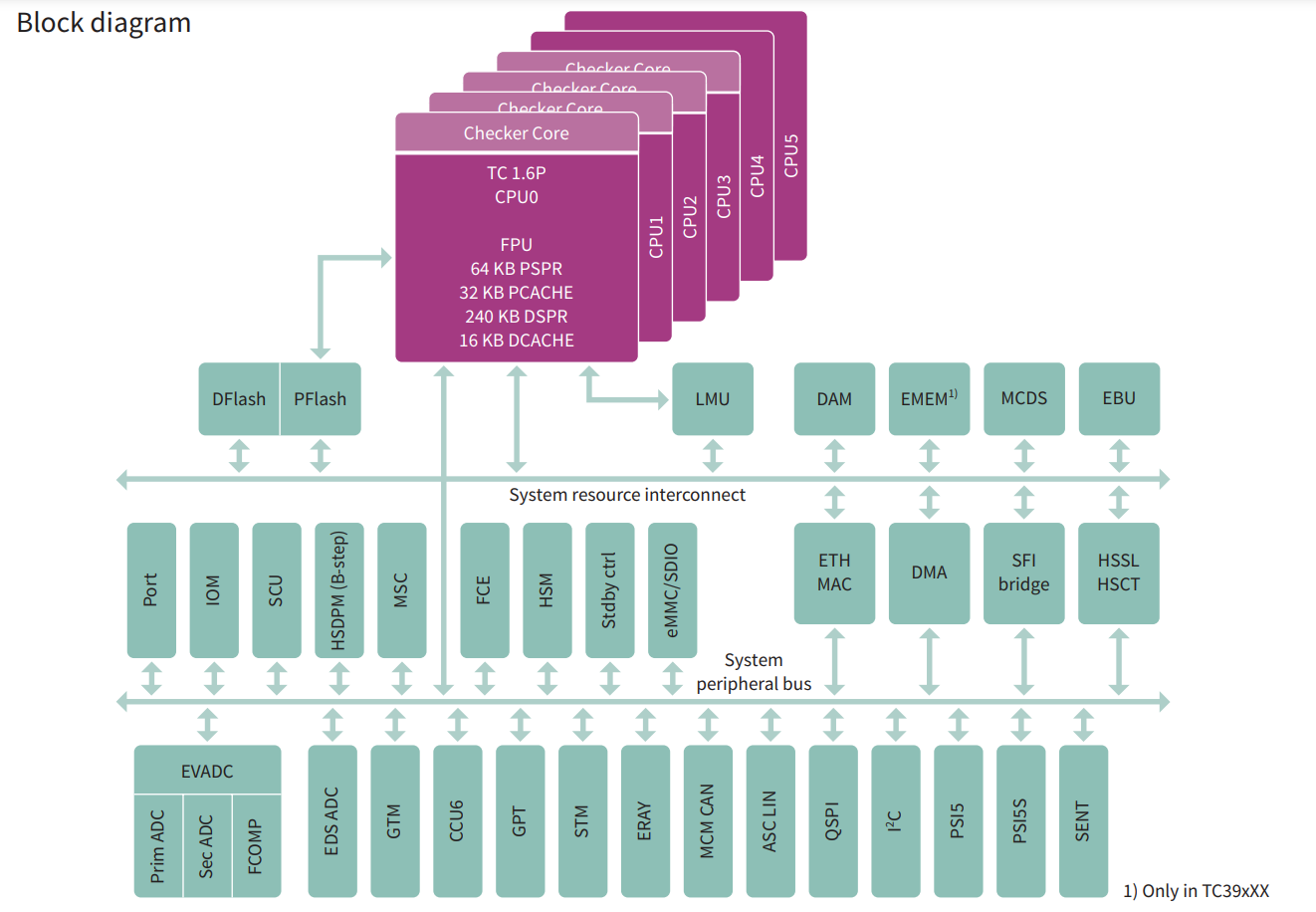

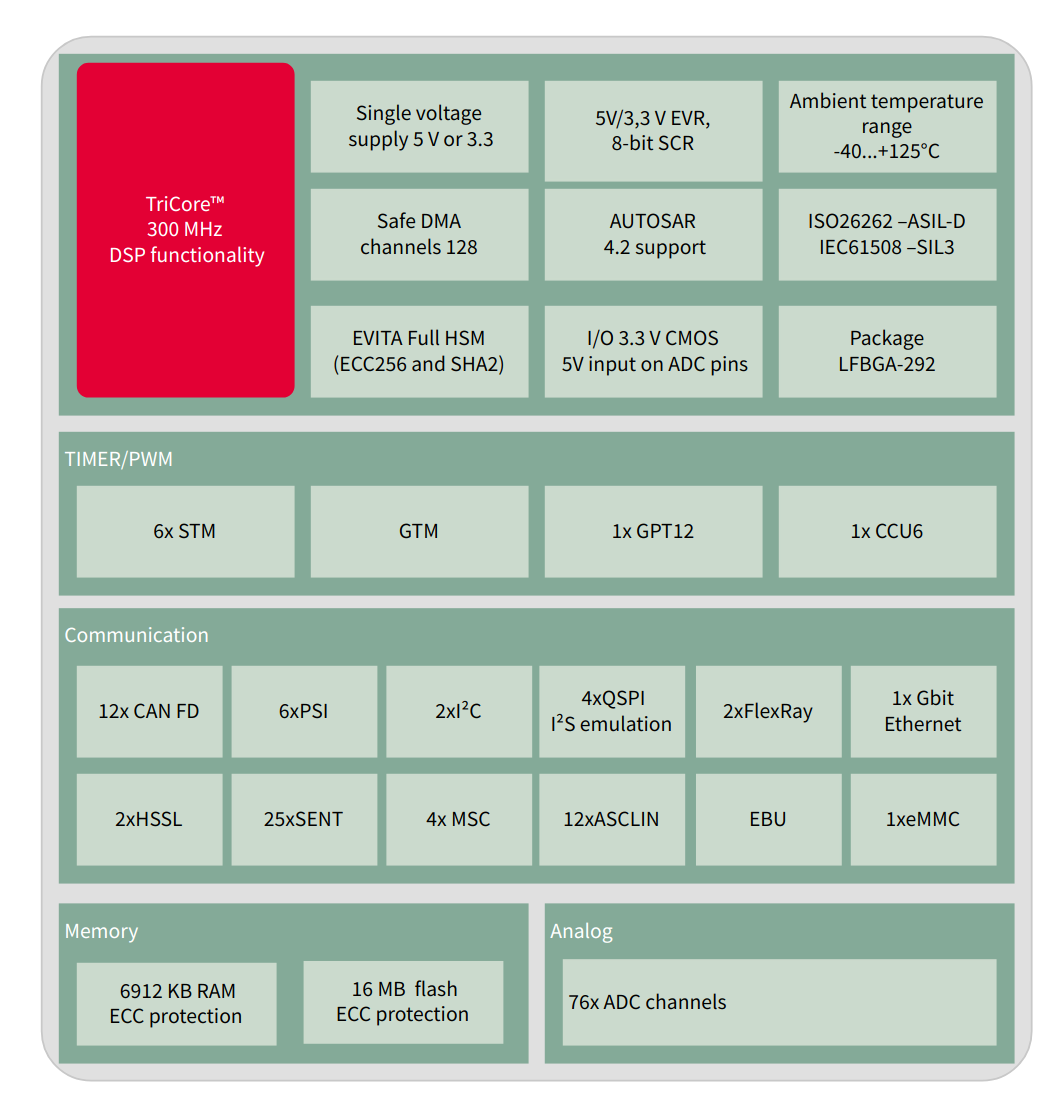

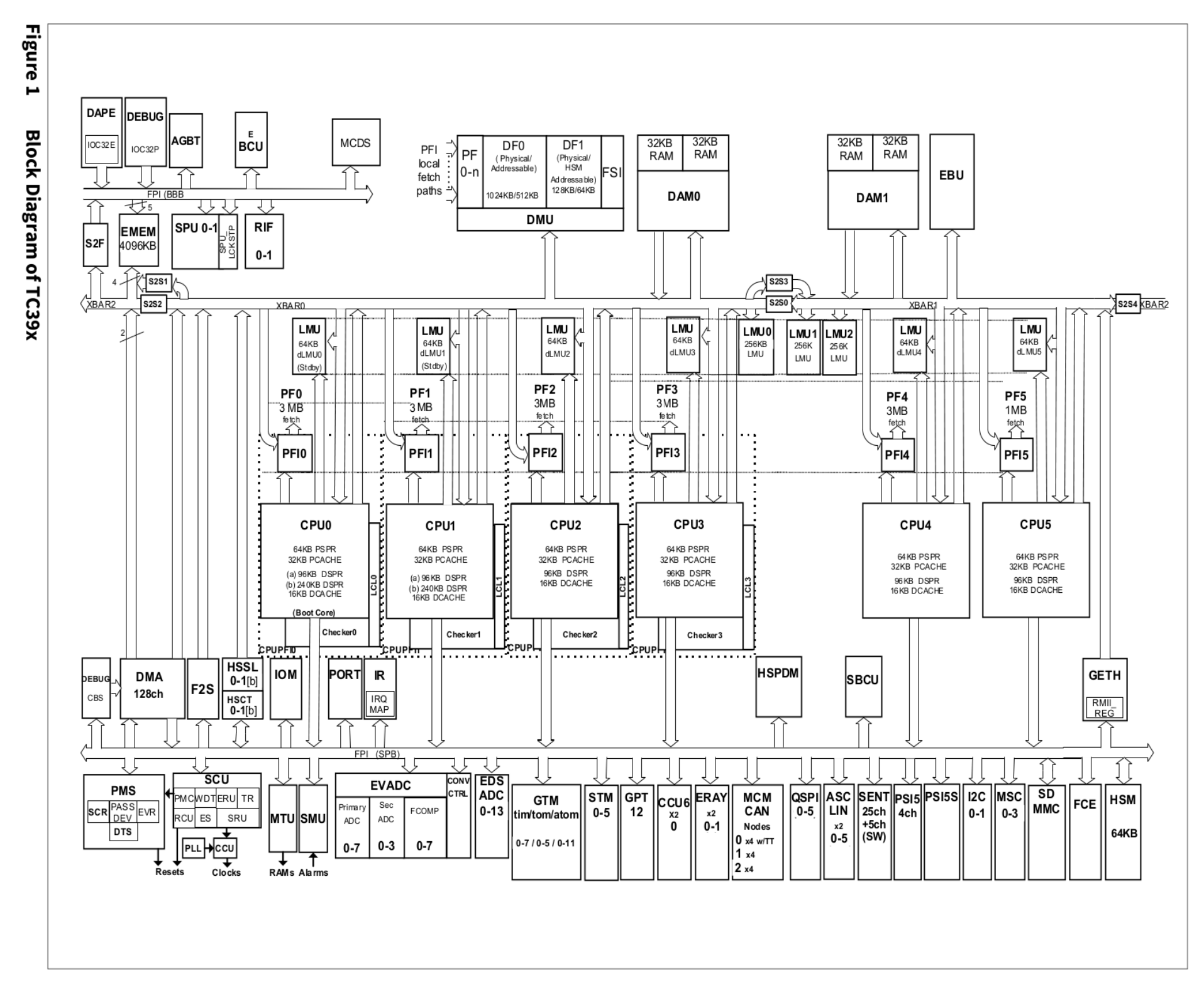

TC397XX:

官方介绍: SAK-TC397XX-256F300S BD

Infineon-AURIX_TC3xx_Architecture_all-UserManual-v01_00-EN.pdf

Infineon-AURIX_TC39x-UserManual-v02_00-EN.pdf

硬件特性:

TriCore™ TC397xx是32位高性能的微控制器,广泛应用于汽车和其他要求高可靠性和高性能的领域。以下是其主要特性:

处理器架构:

- 配备6个TriCore™(TC1.6.2)核心,主频为300 MHz,其中包括4个附加的检查核心,提供4000 DMIPS(Dhrystone MIPS)。

浮点与定点支持:

- 所有核心都支持浮点运算和定点运算,提供灵活的计算能力。

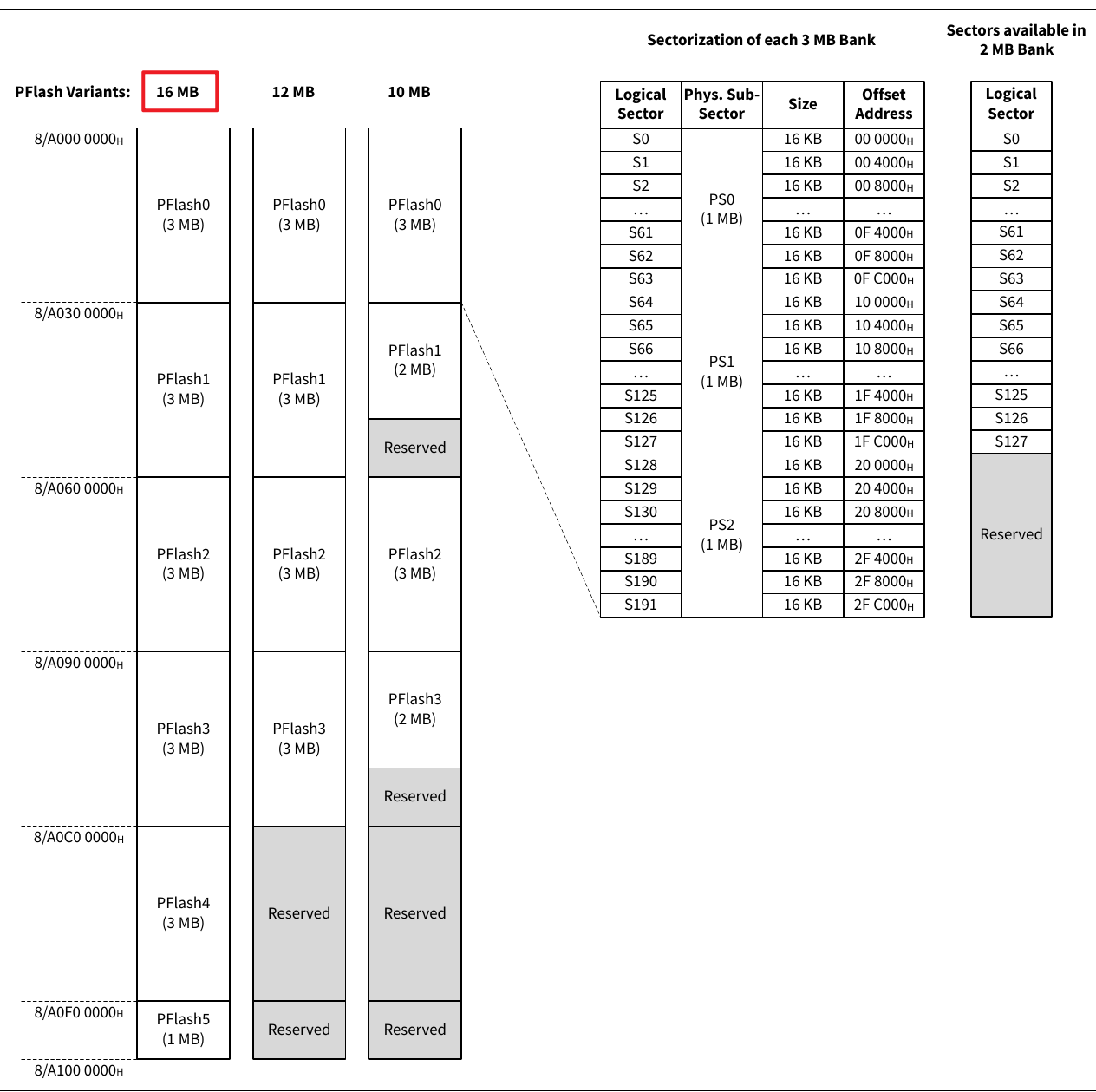

RAM/ROM:

- 16 MB flash,支持ECC(错误更正码)保护。

umbrella (5 x 3 MB, 1 x 1 MB)1. 高达6.9 MB SRAM,支持ECC保护,增强数据可靠性。

通信接口:

- 1 Gbit以太网接口。

- 12个CAN FD接口,用于高带宽的控制器局域网络通信。

- 2个FlexRay接口,支持高速车载通信。

- 12个ASCLIN(异步串行通信接口),适用于多种串行通信需求。

- 6个QSPI接口(四线串行外设接口),用于高速外部存储。

- 2个I²C接口,支持多主设备和多从设备的串行通信。

- 25个SENT接口(串行增强数字传感器接口),用于传感器数据采集。

- 4个PSI5接口和1个PSI5S接口,支持车载传感器的数据传输。

- 2个HSSLL接口(高速同步串行链路),适用于高速数据传输。

- 4个MSC接口(多功能同步通信),用于多种数据通信需求。

- 1个eMMC/SDIOT接口,支持外部存储扩展。

- 1个I²S仿真接口,用于音频数据传输。

定时器模块:

- 多种冗余和多样化的定时器模块,如GTM(通用定时器模块)、CCU6(计数器控制单元6)、GPT12(通用预分频定时器12),提供精确的时间管理和测量功能。

安全性:

- EVITA Full HSM(硬件安全模块),支持ECC256(椭圆曲线密码学256位密钥)和SHA2(安全散列算法2),提供高级的安全保障。

封装:

- 采用LFBGA-292封装,适合高密度集成。

安全标准:

- 依照ISO 26262/IEC 61508标准进行开发和文档化,支持高达ASIL-D(汽车安全完整性等级D)/SIL3(安全完整性等级3)的安全要求。

AUTOSAR支持:

- 支持AUTOSAR 4.2(汽车开放系统架构),用于车载软件的标准化开发。

可选浮点单元 (FPU) 和内存管理单元 (MMU)

电源供应:

- 单电压供电,支持5 V或3.3 V电压输入。

温度范围:

- 工作温度范围为-40°C到125°C,适合极端环境下的应用。

优势:

最佳性能,支持ASIL-D设计

- ASIL-D合规性:TC397xx微控制器提供了顶级的性能,能够支持达到ASIL-D安全标准的设计。ASIL-D是ISO 26262标准中最高的汽车安全完整性等级,确保汽车应用的最高安全水平。

向下兼容,适配成本更低的AURIX™ TC3xx微控制器

- 成本效益:TC397xx微控制器可以向下兼容,适配较低成本的AURIX™ TC3xx系列微控制器。这种向下兼容性意味着可以在不同成本级别的产品中使用相似的硬件架构,帮助降低整体系统成本,同时保留核心功能和性能。

支持A/B交换的软件更新

- 远程更新支持:TC397xx支持A/B交换的软件更新机制,这允许在系统运行时进行安全的软件更新。A/B交换的方式可以在不影响系统正常运行的情况下完成软件更新,提升系统的可靠性和安全性。这种支持对汽车系统的维护和升级非常重要,尤其是在需要远程更新的情况下。

从AURIX™第一代产品的易迁移

- 兼容性:TC397xx微控制器与AURIX™第一代产品在软件和硬件方面具有兼容性,使得从早期版本的AURIX™微控制器迁移到TC397xx变得更为简便。这样的兼容性不仅减少了开发时间和成本,还可以确保现有系统的平稳过渡

Flash

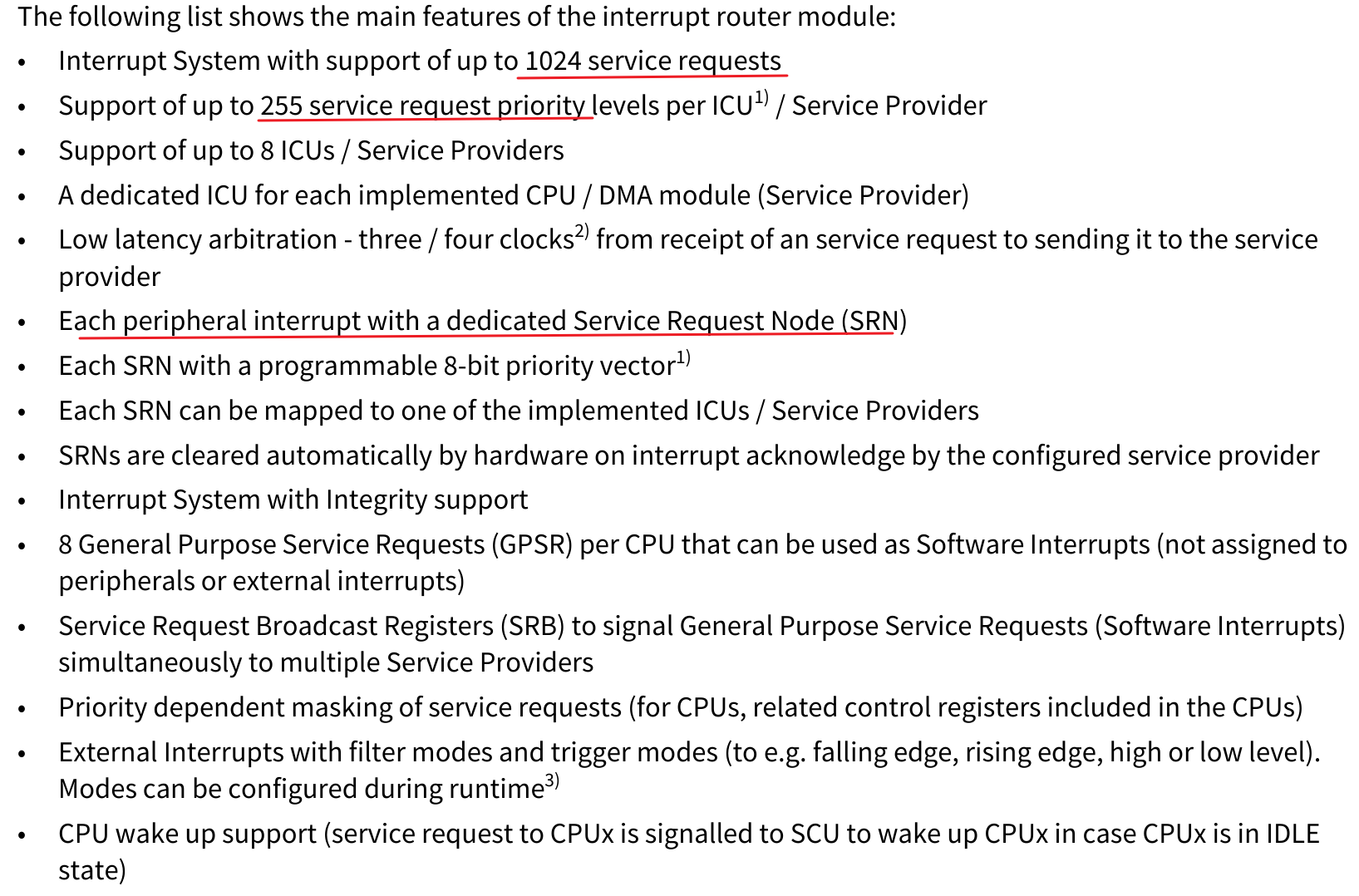

中断

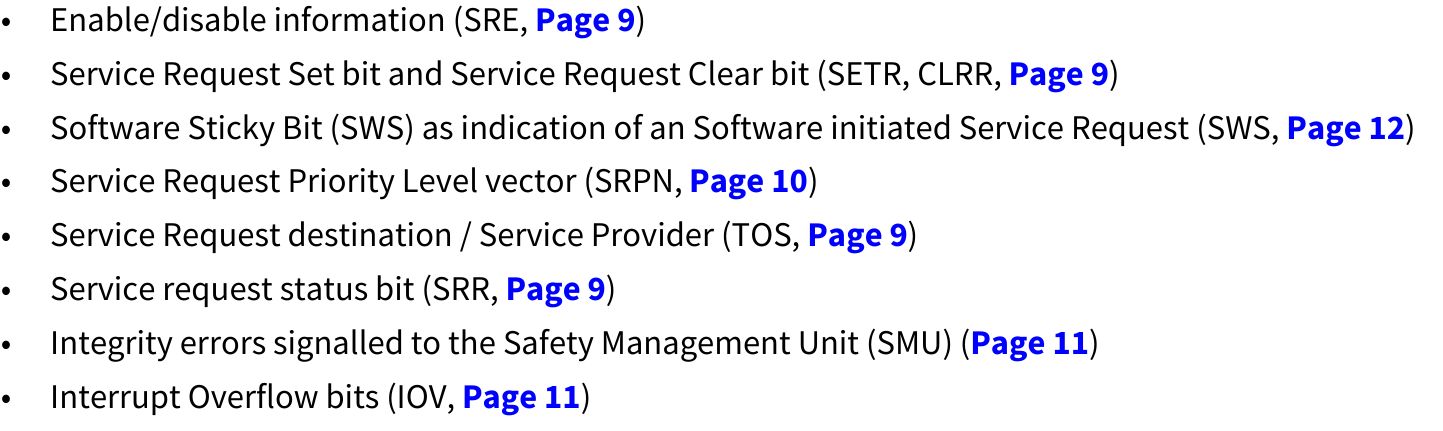

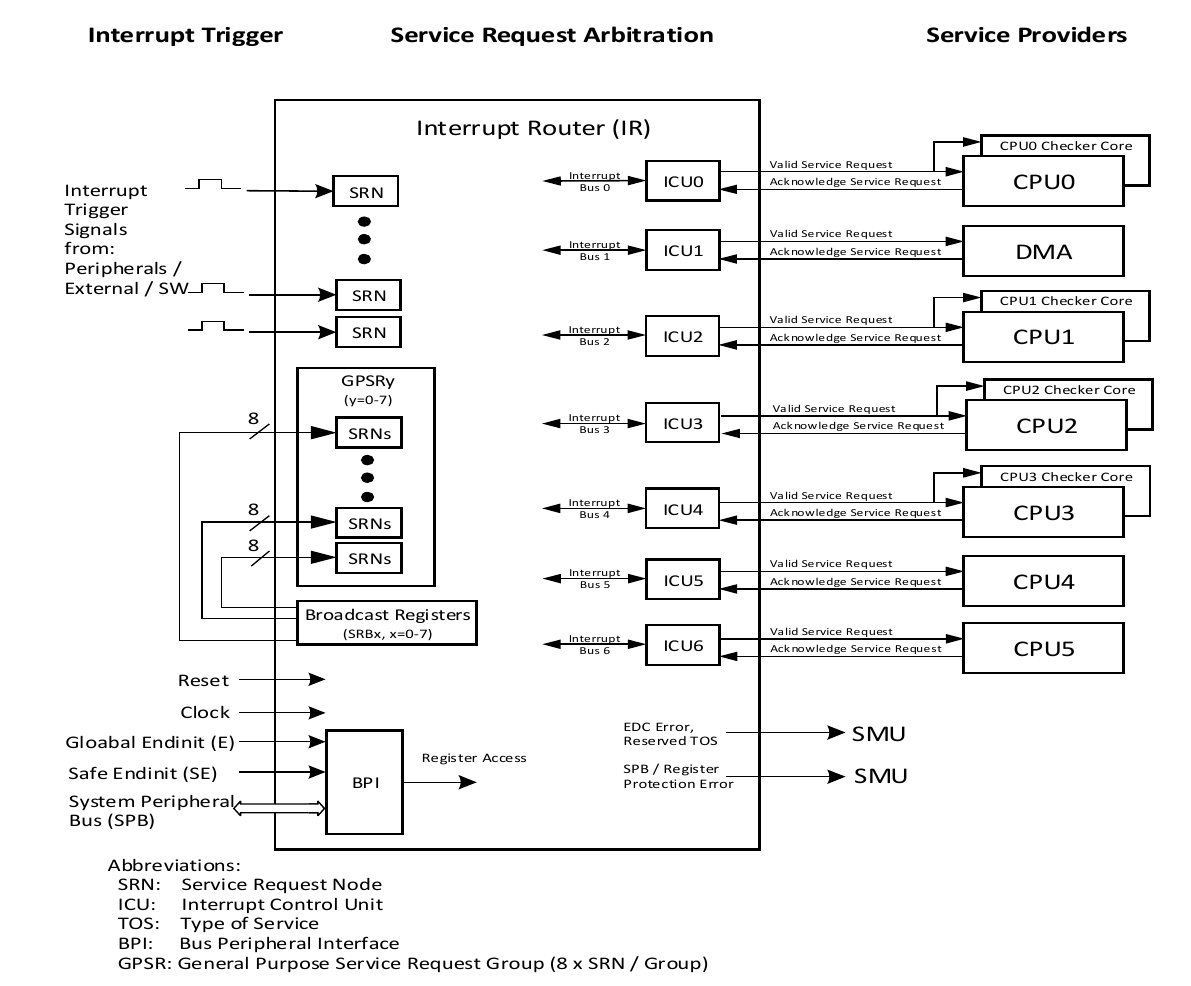

中断请求可以由CPU或DMA模块来处理,在文档中被称为“ 服务请求 ”而不是“中断请求”,因为它们可以由任一服务提供者处理。

中断系统是在中断路由器(IR)模块中实现的,该模块包括服务请求节点(SRNs)、中断控制单元(ICUs),以及一些支持软件开发的附加功能。

如下图所示,每个可以产生服务请求的模块都连接到 IR 模块中的一个或多个服务请求节点(SRNs)。IR 模块还包括几个通用的服务请求节点(SRNs),即软件触发中断

每个SRN都包含一个SRC(Service Request Control Register),用来配置服务请求的优先级、映射到的服务提供者等。每个SRN都连接到中断路由器模块中的所有ICUs,而SRN的控制寄存器设置则定义了服务请求的目标服务提供者和优先级。

每个ICU负责在映射到该ICU的多个服务请求之间进行中断仲裁。ICU在仲裁轮中选择一个有效的获胜服务请求/SRN,并将其提供给服务提供者(CPU或DMA模块)。服务提供者在处理服务请求时,向ICU反馈当前正在处理的服务请求。

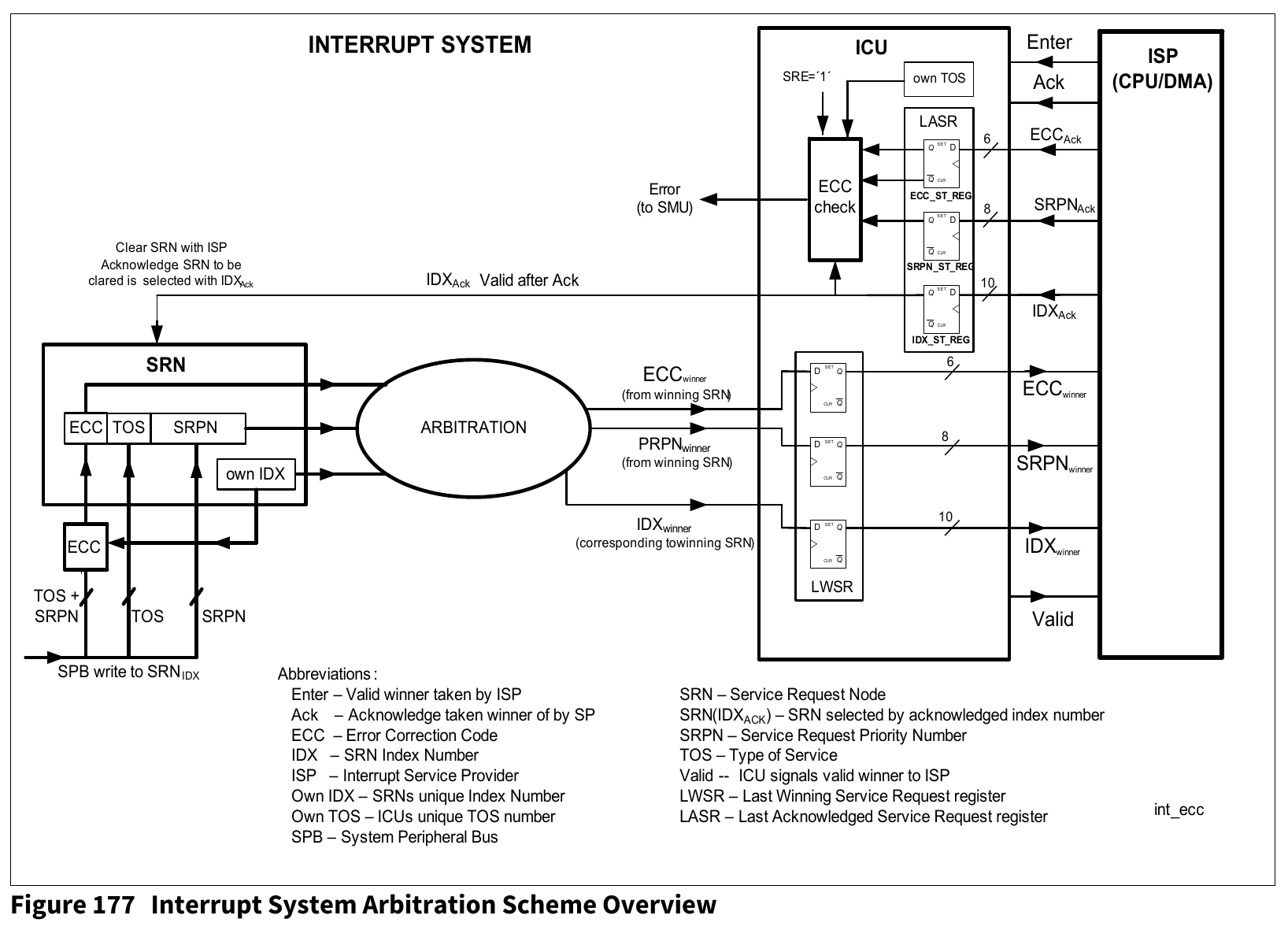

中断仲裁

每个中断模块中的中断控制单元 (ICU) 都有自己独立的中断总线。每个服务请求节点 (SRN) 都可以通过在SRC.TOS 位字段中设置,将其映射到相关的 ICU / 中断总线上,从而将该服务请求节点定向到特定的服务提供者

SRC.TOS: Type of Service Control ( cpu0-5, dma )

SRC.SRE: Service Request Enable (1:enabled)

当第一个服务请求pending时,相关的中断总线将启动第一次仲裁过程。相关的中断控制单元 (ICU) 提供在上一次仲裁过程中获胜的服务。仲裁过程使用 3-4 个系统外围总线时钟周期来确定具有最高优先级号码 (SRPN) 的待处理服务请求。

在仲裁过程中,中断总线会比较映射到此中断总线(通过 SRC.TOS 设置)的所有待处理服务请求节点 (SRN) 的SRC.SRPN 位字段。仲裁过程中,具有最高优先级号码的待处理服务请求将被识别为获胜者,并且相关的 SRN 服务请求控制寄存器的位字段值(SRPN、ECC 和 SRN 的索引)将提供给 ICU,并传给给服务提供者,然后ICU会收到确认信息,之后进行ECC校验,中断路由模块会将检测到的错误信号发送到安全管理单元 (SMU)(SMU 中的一个位覆盖了所有 SRN 和 ICU 的错误)。

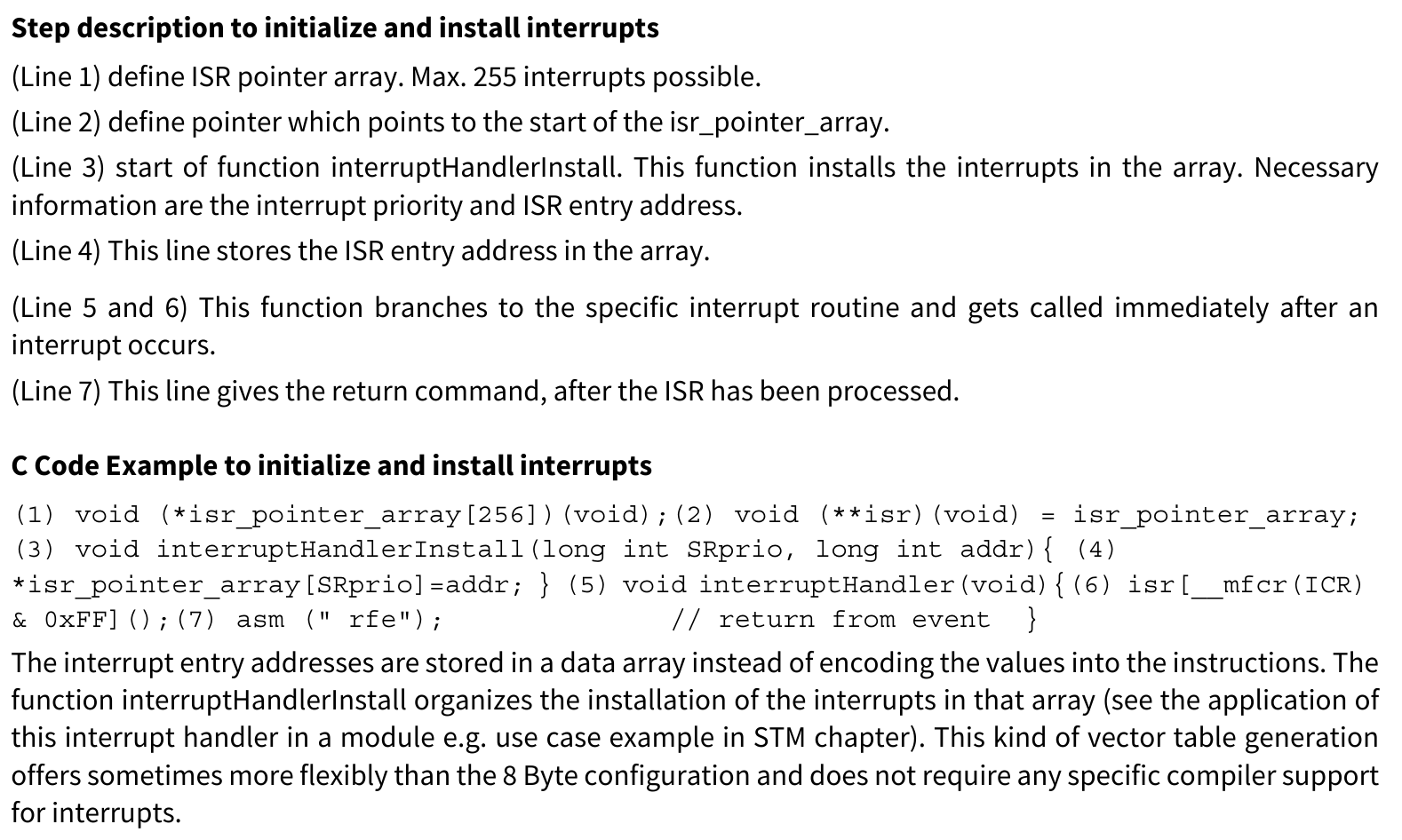

中断配置

如下图中断向量表可以配置32byte,8byte,单地址

中断初始化:

外部中断:

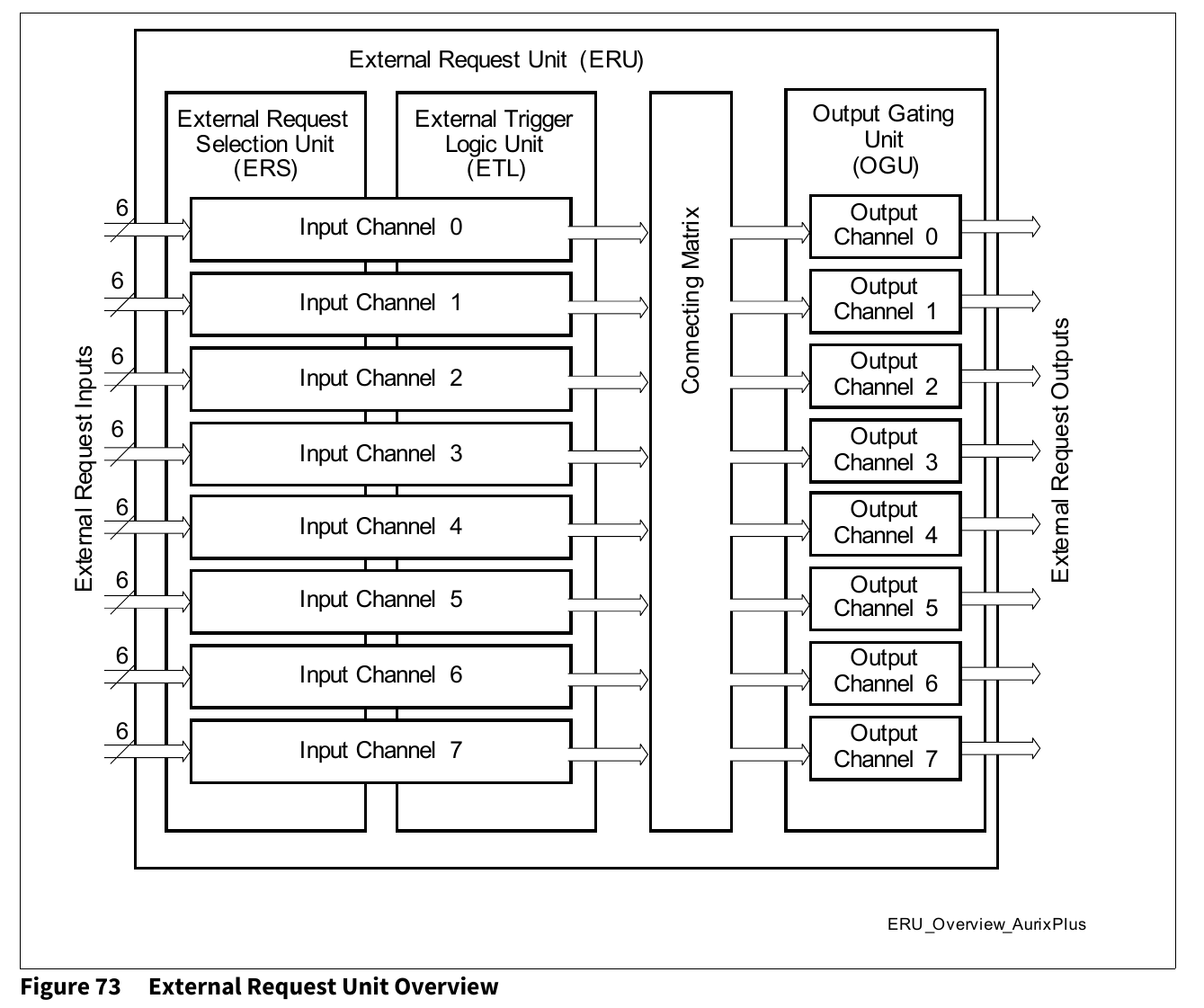

External Request Unit (ERU) 是一个多功能的事件和模式检测单元,其主要功能是根据可选择的触发事件生成中断(例如,当输入引脚上检测到边沿变化时,生成外部中断请求)。此外,ERU还可以将检测到的事件用于其他目标模块,以触发或控制模块特定的操作。

功能列表:

- 生成中断:支持基于不同输入上的可选择触发事件生成中断。

- 8个独立输入通道:用于输入选择和触发或控制功能的条件设定。

- 事件分配矩阵:使用连接矩阵定义输入通道x的事件,这些事件将导致输出通道y的反应。

- 8个独立输出通道:用于事件组合、定义事件的效果,并分配给系统(例如,中断生成、定时器触发等)。

这些功能使ERU成为一个强大的工具,用于检测和响应多种外部信号和事件,在嵌入式系统中具有广泛的应用。

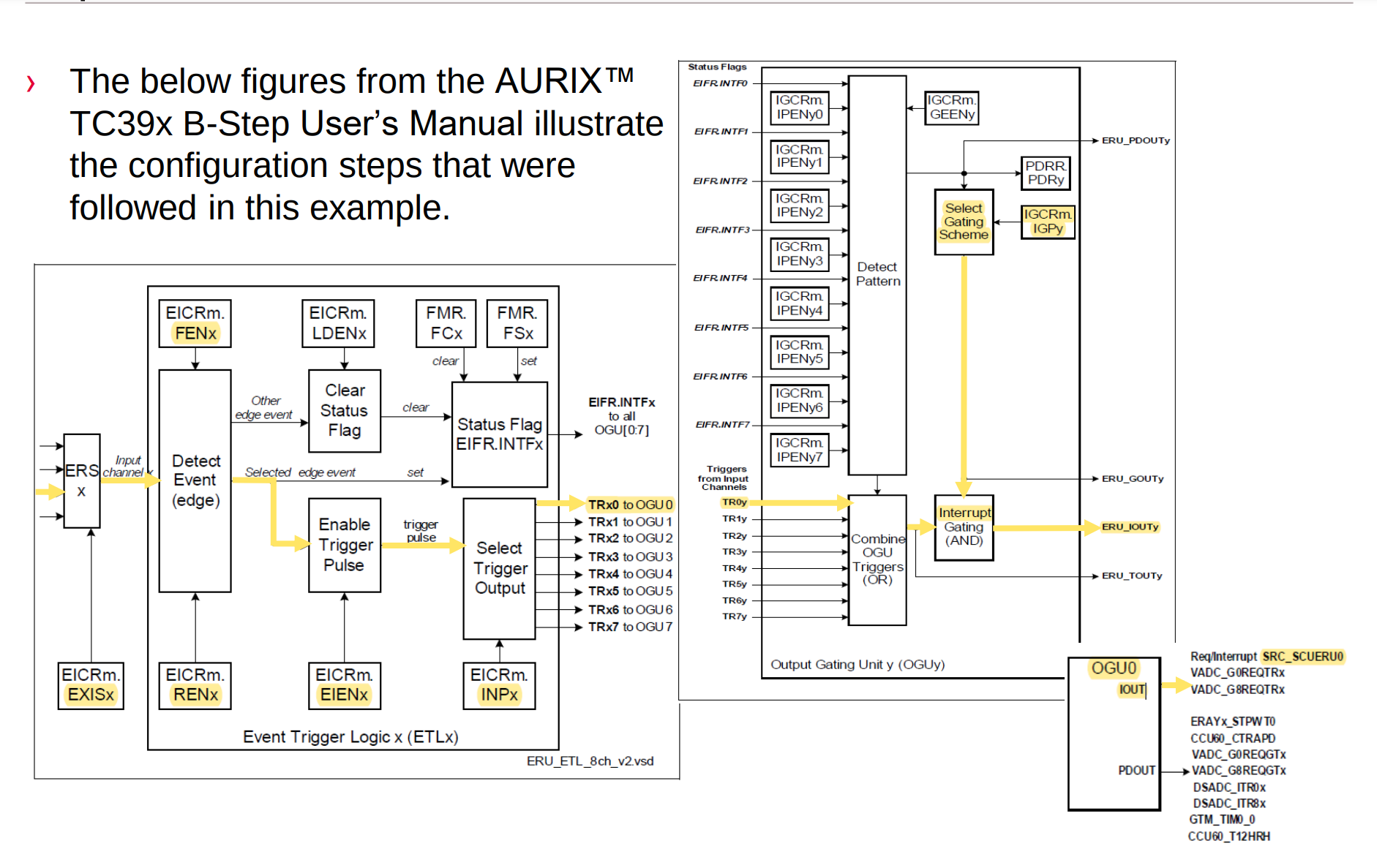

这些任务由以下构建块(building block)处理:

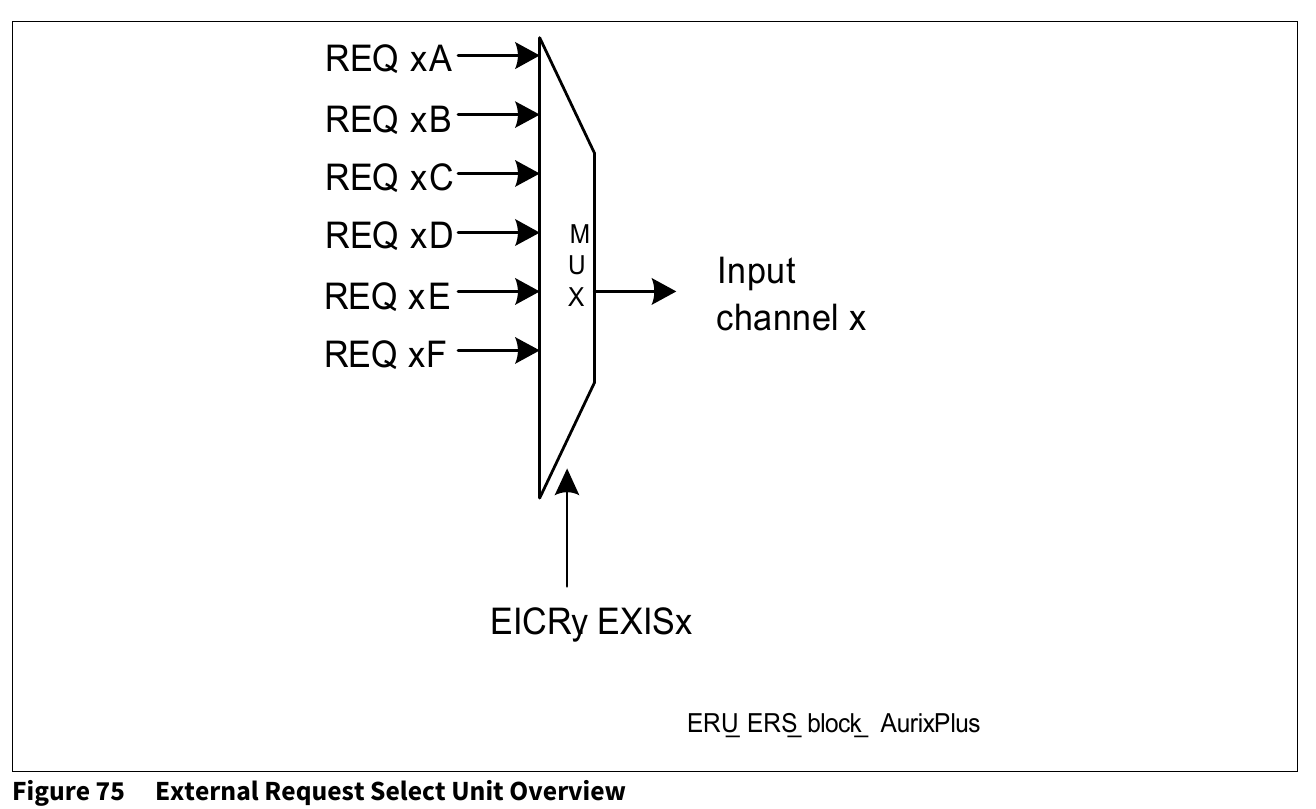

- External Request Select Unit (ERSx), 每个输入通道都有一个外部请求选择单元(ERSx),可以从6个可能的可用输入中选择一个输入向量

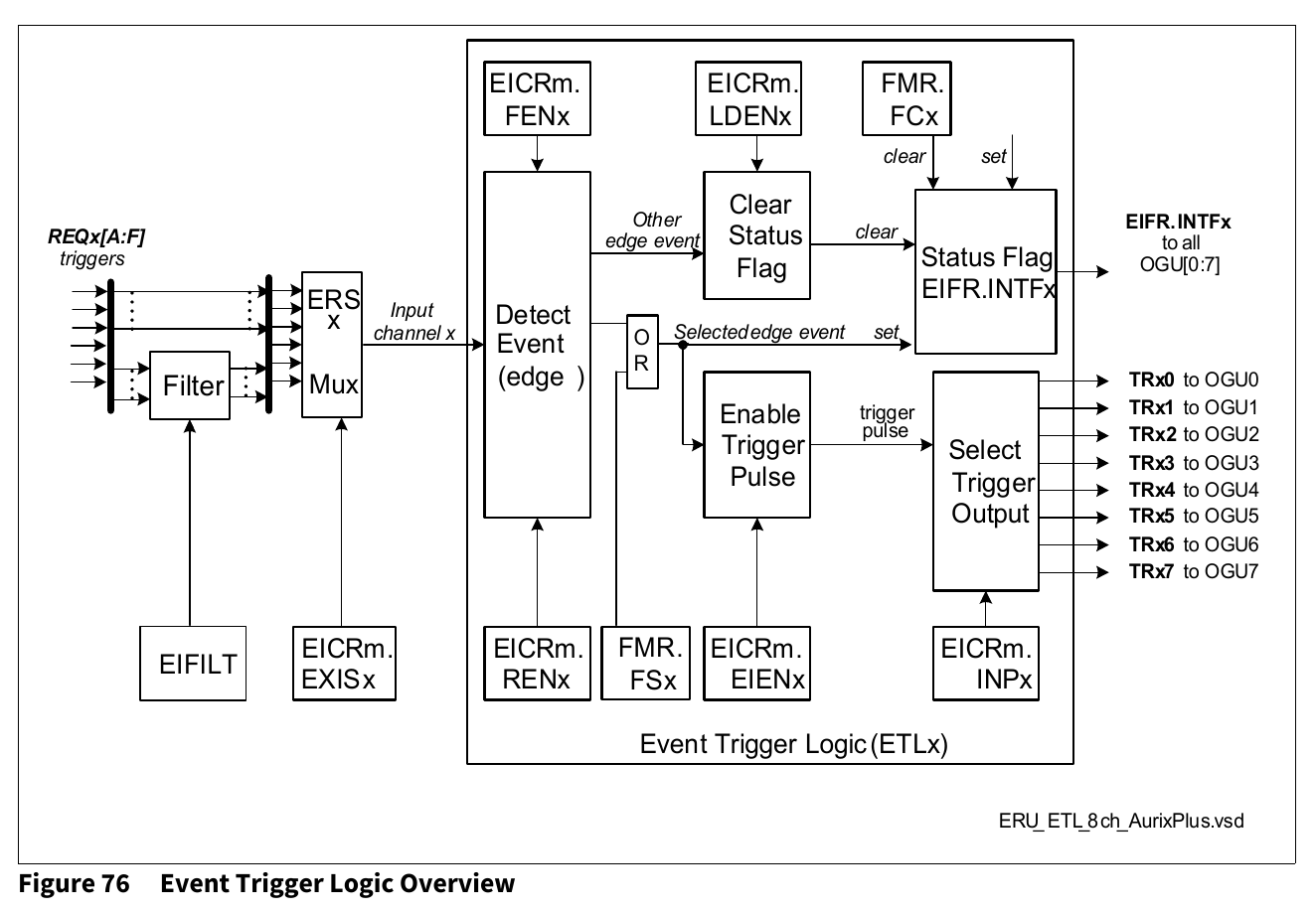

- Event Trigger Logic (ETLx), 每个输入通道的事件触发逻辑(ETLx)允许定义导致触发事件的转换(边缘选择或通过软件),也可以存储此状态. 此处,所选信号的输入电平被转换为事件(检测到事件=置位事件标志,与原始输入信号的极性无关)

- Connecting Matrix, 连接矩阵将输入通道生成的事件和状态标志分配到输出通道

- Output Gating Unit (OGUy), 每个输出通道的输出门控单元(OGUy),结合了可用的触发事件和来自输入通道的状态信息. 一个输入通道的事件可以导致多个输出通道的反应,或者多个输入通道的事件也可以组合成一个输出通道的反应(模式检测). 可以配置不同类型的反应,例如产生中断.

可以从大量输入信号中选择ERU的输入, 这些输入中的16个直接来自输入端口,而其他输入则来自各种外围模块状态信号.

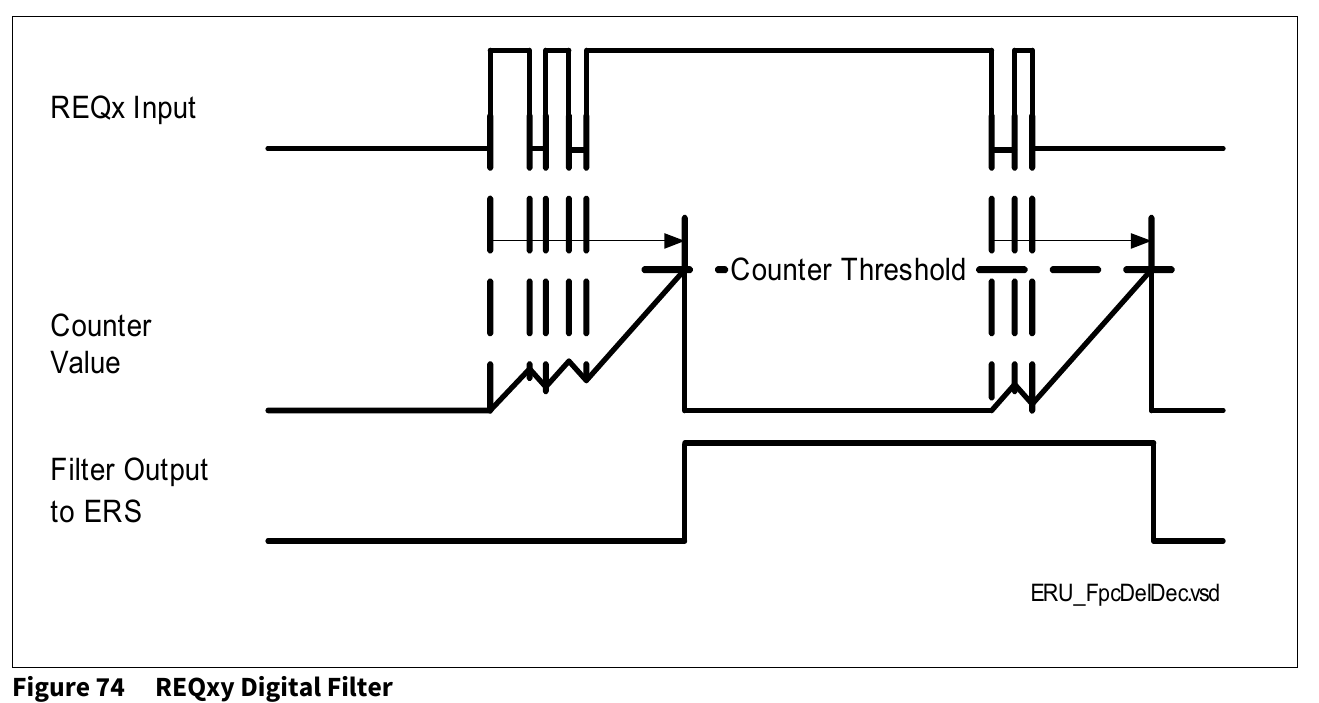

REQxy Digital PORT Input Glitch Filter (FILT), 毛刺滤波器仅在端口(PORTS)可用, 用寄存器EIFILT配置, 用于抑制信号噪声导致PORTS的输入引脚上发生的不必要的快速转换, 类似于延时消抖. 滤波器预分频器可以设置为1到15之间的值,从而提供从10ns ~ >2µs的可能的毛刺特性范围, 通常,3~5 Tfilt的深度就足够了. 默认情况下,它是清除的. 如果清除了DEPTH,则所有过滤器均处于非活动状态:

External Request Selector Unit (ERS):

Event Trigger Logic (ETLx), 事件触发逻辑, 基于边缘检测模块,在该模块中,可以分别启用对上升沿或下降沿的检测. 如果两个使能位都被置位(例如处理触发输入),则两个边沿都会导致触发事件. 四个ETL单元中的每对都有一个关联的EICRy寄存器,该寄存器控制ETL的所有选项(该寄存器还保存关联的ERS单元对的控制位)

ERU_Interrupt_1 for KIT_AURIX_TC397_TFT

如何设置中断向量表,以及中断handler如何放到中断向量表中的

Lcf_Tasking_Tricore_Tc.lsl

1

2#define LCF_TRAPVEC0_START 0x80000100

3#define TRAPTAB0 (LCF_TRAPVEC0_START)

4 "__TRAPTAB_CPU0" := TRAPTAB0;

5

6 group trapvec_tc0 (align = 8, run_addr=LCF_TRAPVEC0_START)

7 {

8 section "trapvec_tc0" (size=0x100, attributes=rx, fill=0)

9 {

10 select "(.text.traptab_cpu0*)"; // 下文代码中配置的

11 }

12 } 1// IfxCpu_Trap.c

2

3#pragma protect on

4#pragma section code "traptab_cpu0"

5

6void IfxCpu_Trap_vectorTable0(void)

7

8#pragma endprotect

9

10| IfxCpu_Trap.o | .text.traptab_cpu0 (27065)| 0x000000f2 | 0x0| .text.traptab_cpu0 (27065) | 0x000000f2 |

11

12Ifx_Ssw_MTCR(CPU_BTV, (unsigned int)__TRAPTAB(0)); 1#define LCF_INTVEC0_START 0x802FE000

2#define INTTAB0 (LCF_INTVEC0_START)

3 "_lc_u_int_tab" = (LCF_INTVEC0_START);

4 "__INTTAB_CPU0" = (LCF_INTVEC0_START);

5

6

7#define IFX_INTERRUPT(isr, vectabNum, prio) IFX_INTERRUPT_INTERNAL(isr, vectabNum, prio)

8#define IFX_INTERRUPT_INTERNAL(isr, vectabNum, prio) void __interrupt(prio) __vector_table(vectabNum) isr(void)

9

10Ifx_Ssw_MTCR(CPU_BIV, (unsigned int)__INTTAB(0));

11

12

13// 中断入口分析

14// 0x8002404c | QSPI0ERR_ISR | 0x63

15// 0x803FE000 + 0x0C60 // .text.inttab0.intvec.063

16 .sdecl '.text.inttab0.intvec.063', CODE AT 0x803fec60

17 .sect '.text.inttab0.intvec.063'

18803fec60 91 20 00 e8 movh.a a14,#0x8002

19803fec64 d9 ee 0c 14 lea a14,[a14]0x404c

20803fec68 dc 0e ji a14参考:

AURIX TC397 SCU 之 ERU 外部中断_scu中断配置-CSDN博客

UCB:6.8 User Configuration Block (UCB)

TriCore™ Embedded Applications Binary Interface (EABI)

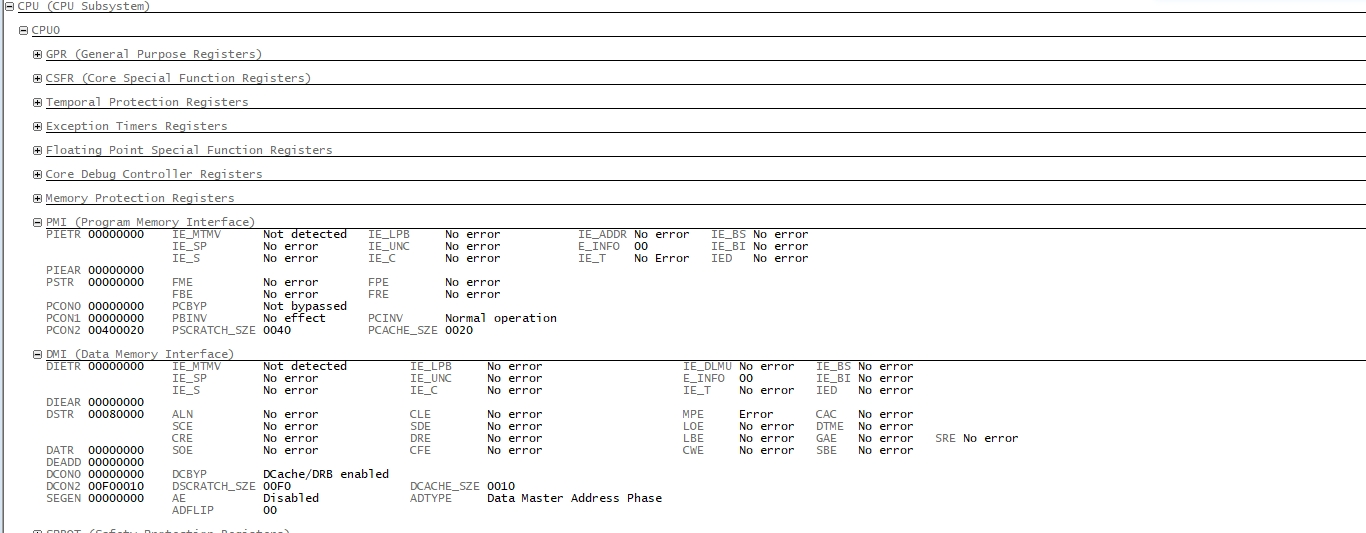

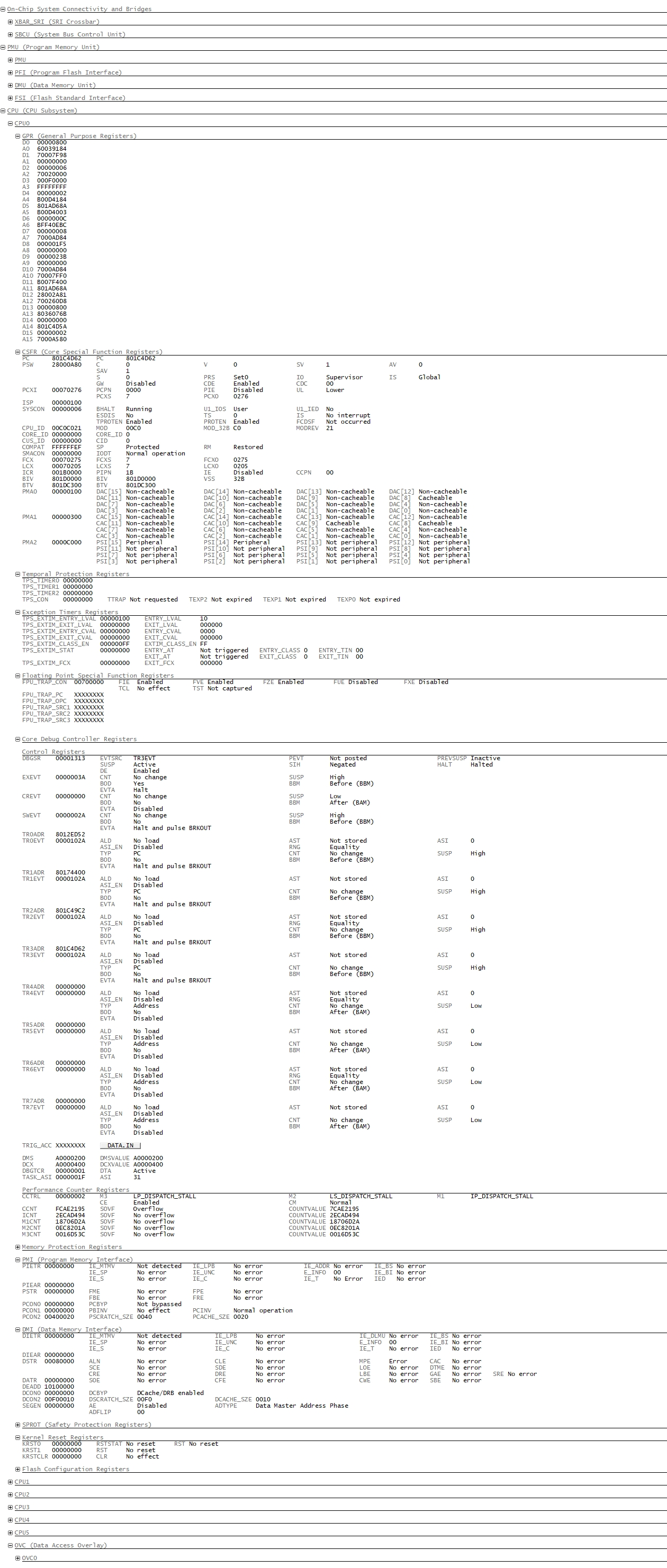

问题定位

访问空指针

DMI->DSTR->MPE : Error

系统寄存器

port多核访问

- Write access enable register 配置

- tc4规范章节4了解

缩略词

展开:

| Acronym | Description |

|---|---|

| ADAS | Advanced Driver Assistance System |

| ADC | Analog-to-Digital Converter |

| ALU | Arithmetic and Logic Unit |

| ASCLIN | Asynchronous/Synchronous Serial Controller with LIN |

| BBB | Back Bone Bus |

| BCU | Bus Control Unit |

| BROM | Boot ROM & Test ROM |

| CAN | Controller Area Network |

| CIF | Camera (and ADC) Interface |

| CCU | Clock Control Unit |

| CPU | Central Processing Unit |

| CRC | Cyclic Redundancy Code |

| CSA | Context Save Area |

| CSFR | Core Special Function Register |

| CCU6 | Capture Compare Unit 6 |

| DAM | Default Application Memory |

| DAP | Device Access Port |

| DAS | Device Access Server |

| DPI | Direct Processor Interface (to Local Flash Bank) |

| DCACHE | Data Cache |

| DFLASH (or DF) | Data Flash Memory |

| DLMU | Direct-connected Local Memory Unit |

| DMA | Direct Memory Access |

| DMBI | Data Memory Bus Interface |

| DMI | Data Memory Interface |

| DMU | Data Memory Unit |

| DRLB | Data Read Line Buffer |

| DSPR | Data Scratchpad RAM |

| EBU | External Bus Interface |

| ECC | Error Correction Code |

| ED | Emulation Device |

| EDSADC | Enhanced Delta-Sigma Analog to Digital Converter |

| EVADC | Enhanced Versatile Analog-to-Digital Converter |

| EMI | Electro-Magnetic Interference |

| ERAY | Flexray Controller |

| EtherMAC | Ethernet Media Access Controller |

| EVR | Embedded Voltage Regulator |

| FCE | Flexible CRC Engine |

| FCOMP | Fast Comparator |

| FM-PLL | PLL with Frequency Modulation support |

| FPI | Flexible Peripheral Interconnect (Bus protocol) |

| FPU | Floating Point Unit |

| FSM | Finite State Machine |

| GPIO | General Purpose Input/Output |

| GPT12 | General Purpose Timer 12 |

| GTM | Generic Timer Module |

| HSM | Hardware Security Module |

| HSPDM | High Speed Pulse Density Modulator |

| HSSL | High Speed Serial Link |

| I2C | Inter-Integrated Circuit Controller |

| I/O | Input / Output |

| IOM | I/O Monitor Unit |

| IR | Interrupt Router |

| JTAG | Joint Test Action Group = IEEE1149.1 |

| LMU | Local Bus Memory Unit |

| MBIST | Memory Build In Self Test |

| MMU | Memory Management Unit |

| MSB | Most Significant Bit |

| MSC | Micro Second Channel |

| MTU | Memory Test Unit |

| MCMCAN | CAN controller |

| NC | Not Connected |

| NMI | Non-Maskable Interrupt |

| NVM | Non Volatile Memory |

| OCDS | On-Chip Debug Support |

| OVRAM | Overlay Memory |

| PLL | Phase Locked Loop |

| PCACHE | Program Cache |

| PD | Production Device |

| PFI | Program Flash Interface |

| PFLASH (or PF) | Program Flash Memory |

| PMBI | Program Memory Bus Interface |

| PMI | Program Memory Interface |

| PMS | Power Management System |

| PSI5 | Peripheral Sensor Interface |

| PSI5-S | Peripheral Sensor Interface with Serial Interface to Phy |

| PSPR | Program Scratchpad RAM |

| QSPI | Queued SPI Controller |

| RAM | Random Access Memory |

| RCU | Reset Control Unit |

| RIF | Radar Interface |

| RISC | Reduced Instruction Set Computing |

| SBCU | System Peripheral Bus Control Unit |

| SCU | System Control Unit |

| SCR | Standby Controller |

| SENT | Single Edge Nibble Transmission |

| SFR | Special Function Register |

| SMU | Safety Management Unit |

| SPB | System Peripheral Bus (based on FPI protocol) |

| SPU | Signal Processing Unit |

| SPD | Single Pin DAP |

| SPI | Synchronous Serial Controller |

| SRI | Shared Resource Interconnect |

| SRAM | Static Data Memory |

| SRN | Service Request Node |

| STM | System Timer |

| SWD | Supply Watchdog |

| TC1.6.2P | TriCore CPU TC1.6.2P |

| UCB | User Configuration Block |

| WDT | Watchdog Timer |

| XBar, XBar_SRI | Cross Bar Interconnect, based on the Shared Resource Interconnect protocol |

Infineon-TC2xx_EABI-UM-v02_09-EN.pdf ↩︎

PCXI(Previous Context Information register): 保存任务上下文信息

↩︎Field Bits Type Description PCPN [29:22] rw Previous CPU PriorityNumber PIE 21 rw Previous Interrupt Enable (ICR.IE) UL 20 rw 0:Lower, 1:Upper Context PCXS [19:16] rw PCX Segment Address PCXO [15:0] rw Previous Context Pointer Offset PSW (Program Status Word): 记录处理器状态、保护模式等

Field Bits Type Description USB [31:24] rw User Status BitsPRS[2] 15 - Protection Register Set bit[2] S 14 rw Safety Task Identifier PRS[1:0] [13:12] rw Protection Register Set bits[1:0] IO [11:10] rw Access Privilege Level ControlIS 9 rw 0:User Stack, 1: Shared Global Stack GW 8 rw Global Address Register Write Permission CDE 7 rw Call Depth Count Enable CDC [6:0] rw Call Depth Counter (0-64) User Status Bits:

Field Bits Type Description C 31 rw Carry V 30 rw Overflow SV 29 rw Sticky Overflow AV 28 rw Advance Overflow SAV 27 rw Sticky Advance Overflow RES [26:24] - Reserved Field

↩︎Access Privilege Level Control:

00: User-0 Mode, No peripheral access

01: User-1 Mode, Regular peripheral access

10: Supervisor Mode, Enables access to all peripheral devicesBIV(Base Interrupt Vector Table Pointer): 中断向量地址

↩︎Field Bits Type Description BIV [31:1] rw Base Address of Interrupt Vector Table VSS 0 rw Vector Spacing Selec (0:32byte,1:8byte) BTV(Base Trap Vector Table Pointer): trap异常地址

↩︎Field Bits Type Description BIV [31:1] rw Base Address of Trap Vector Table RES 0 - Reserved ICR(ICU Interrupt Control Register): 中断控制寄存器

↩︎Field Bits Type Description PIPN [23:16] rh Pending Interrupt Priority Number

0:no pending, 1:lower priorityIE 15 rwh Global Interrupt Enable Bit

0:全局关中断,1:全局开中断CCPN [7:0] rwh Current CPU Priority Number

评论